# 中性点クランプ型3レベルインバータのコンデンサ最小容量設計法

## 田中 孝明\* 伊東 淳一(長岡技術科学大学)

Optimal Design of Capacitance Volume for a Neutral-Point-Clamped Three-Level Inverter Takaaki Tanaka\*, Jun-ichi Itoh, (Nagaoka University of Technology)

A problem of Neutral-point-clamped-inverters is voltage fluctuation of the neutral point capacitor. At this measure, various suppression methods for the voltage fluctuation have been proposed. However, the suppression methods are constrained by voltage limitation of the inverter and load power factor. Hence, capacitance value to keep the neutral point voltage is larger than the that of ideal value.

In this paper, we discuss the minimum value of the neutral point capacitor when the voltage fluctuation suppression method is applied with voltage command saturation. The relationship among the input and output voltage conditions and capacitance value in static state are shown clearly. In addition, the optimal design of capacitance value basis on this analysis is proposed. The validity of the design method is confirmed by experimental results.

**キーワード**: 中性点クランプ型, インバータ, 中性点電位, コンデンサ容量, 設計 (Neutral-point-clamped, Inverter, Neutral point voltage, Capacitance, Design)

#### 1. はじめに

中性点クランプ型 3 レベルインバータ $^{[1]}$  (以下は 3 レベルインバータと記す。)は 3 レベルの相電圧を出力可能であることから高調波を低減できる利点を持つ。この利点により①フィルタの小型化,②キャリア周波数をさげても高調波の発生を 2 レベルインバータと同程度に抑制できる,③低耐圧素子を用いて高い電圧を出力できることから,鉄道車両などのモータドライブや UPS に用いられてきた $^{[2][3]}$ 。その一方で 3 レベルの出力に必要な中性点電圧は 2 つのコンデンサを直列に接続し,その中点する。負荷や出力条件によって,中性点電圧は出力周波数の 3 倍で脈動し,これは高調波や負荷がモータの場合はトルク脈動が発生する原因となる。この対策としては中性点電圧の脈動を抑制する制御(以下は脈動抑制制御と記す。)の適用が有用である $^{[4\sim7]}$ 。

これまでに種々の脈動抑制制御法が提案されているが、それらの原理は2つに大別できる。1つはキャリア比較変調に適用可能な方式である[4][6]。本方式は各相電圧指令値に適切なゼロ相電圧指令値を重畳することで本来流れるはずの中性点電流を抑制することで中性点電圧脈動を抑制する。もう一つは空間ベクトル変調に適用可能な方式である[5][7]。本方式は中性点電圧を用いる出力ベクトルの内、出力に対しては同じベクトルであっても中性点に流れる電流の方向が逆である対のベクトルを利用する。このベクトルの時間

比を調節することで脈動抑制制御を実現する。

しかしながら、いずれの方式も変調率や力率の値によっては電圧変動を補償できず、すべての電圧レンジで完全に中点電位を抑制できない。したがって、電圧脈動の抑制の観点からコンデンサ容量を経験的に大きく設計する必要がある。また、この電圧脈動幅は変調率や負荷力率、負荷電流といった入出力条件によって大きく異なり、3レベルインバータをモータドライブに適用する場合を例にとるとその使用用途によって必要なコンデンサ容量が大きく異なる。ただし、必要以上のコンデンサ容量の増加は不必要なコストや回路体積の増加を招く。したがって、入出力条件に応じたコンデンサ容量設計法が必要である。

筆者らはこれまでに文献[4]で提案されたキャリア比較変調ベースの脈動抑制制御法を適用した場合の中性点電圧の解析手法を用いて、定常状態における入出力条件とコンデンサ容量の理論的に示した[8]。本論文では、3 レベルインバータのコンデンサ容量最小化を目的として、これまで検討した解析結果を基に、実験を行い、実験により妥当性を確認する。さらにこの関係を用いて PM モータを  $i_d$  = 0 で制御した場合の速度ートルクカーブ(NT 線図)上で、動作ポイントを定義し、各動作ポイントにおけるコンデンサ容量設計指針を示す。

まず、出力周波数の3倍で発生する中性点電位変動の抑制制御法について述べ、次に電圧飽和や負荷力率、動作条

件を考慮したコンデンサの決定方法を示す。最後に 1kW の 試作機により検討した理論限界と実験結果との比較を行 い、妥当性について示す。

## 2. 3 レベルインバータ

#### 〈2·1〉 主回路構成

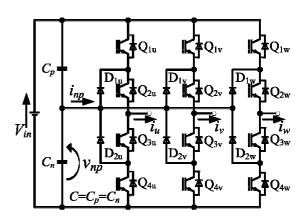

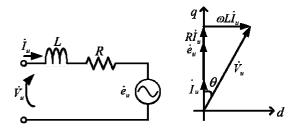

図1に3 レベルインバータの回路構成を示す。3 レベルの相電圧を得るために各相に2 つのスイッチ素子  $Q_{2x}$ ,  $Q_{3x}$  とクランプダイオード  $D_{1x}$ ,  $D_{2x}$  (x はu, v, w のいずれかを意味する。) が追加されている。これらのスイッチ素子を介して2 つのコンデンサの中点から得られる中性点電圧を適切なタイミングで負荷に供給することで,高調波の少ない入出力波形が得られる。さらに,1 アームあたり4 つのスイッチ素子が直列接続された構成となることから,従来の2 レベルインバータと比較して各スイッチ素子の耐圧を半減できる利点も持つ。3 レベルインバータのPWM 方式は多数存在するが,ここではユニポーラ変調を用いる[9]。

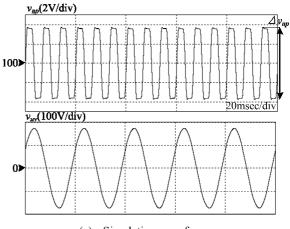

## 〈2·2〉 脈動抑制制御

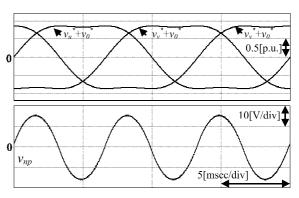

図 2 に電圧利用率の向上を図るために出力周波数の 3 倍高調波を注入した各相電圧指令値と  $v_{np}$  の波形を示す。シミュレーション条件は変調率 a=1.00,負荷力率  $\cos \theta$ =0.80,相電流  $I_u$ =10A,コンデンサ容量 C=200 $\mu$ F である。図 2(a)より中性点電圧は出力周波数の 3 倍で脈動していることを確認できる。この脈動を抑制するために文献[4]に示されている脈動抑制制御を適用する。 $D_{u0}$ ,  $D_{v0}$ ,  $D_{w0}$  を各相の中性点に接続されたスイッチのデューティ, $i_u$ ,  $i_v$ ,  $i_w$  を各相の電流値とすれば,中性点電流  $i_{mn}$  i(1)式にて表せる。

$$i_{np} = D_{u0} \times i_u + D_{v0} \times i_v + D_{w0} \times i_w \dots (1)$$

ここで、 $v_u^*$ ,  $v_v^*$ ,  $v_w^*$ を各相電圧指令、 $v_0^*$ を各相電圧指令に重畳するオフセット値とし、キャリア周波数が出力周波数に比べ、十分高いとすれば、 $D_{u0}$ ,  $D_{v0}$ ,  $D_{v0}$  は(2)式にて表せる。

$$\begin{cases} D_{u0} = 1 - \left| v_u^* + v_0^* \right| \\ D_{v0} = 1 - \left| v_v^* + v_0^* \right| & \dots \\ D_{w0} = 1 - \left| v_w^* + v_0^* \right| \end{cases}$$

(2)

(2)式を(1)式に代入することで中性点を流れる電流  $i_{np}$  の (3)式が得られる。(3)式を解いて  $i_{np}=0$  となる  $v_0^*$ を各相電圧指令に重畳することで脈動抑制制御を実現する。

$$i_{np} = \left(1 - \left|v_{u}^{*} + v_{0}^{*}\right|\right) \times i_{u} + \left(1 - \left|v_{v}^{*} + v_{0}^{*}\right|\right) \times i_{v} + \left(1 - \left|v_{w}^{*} + v_{0}^{*}\right|\right) \times i_{w} \dots (3)$$

図 2(b)に脈動抑制制御を適用した場合の中性点電圧のシミュレーション波形を示す。電圧脈動幅  $\Delta v_{np}$  は 30V から 20V 程度に抑制されている。しかし,完全にゼロとはなっていない。この残存した脈動は  $i_{np}$  をゼロにするために必要な  $v_{0}^{*}$  を重畳した相電圧指令がインバータ出力電圧限界値を超えることに起因する。つまり,変調率が高いとき,電圧脈動は完全には抑制できなくなり,さらなる抑制にはコンデンサ容量を大きく設計する必要がある。

Fig. 1. Circuit configuration of 3-level inverter.

(a) Without suppression control.

(b) With suppression control.

Fig. 2. The effect of voltage fluctuation suppression control

(Upper: Each phase voltage command, Lower: Neutral point voltage)

### 3. コンデンサの最小容量設計法

#### (3·1) 入出力条件とコンデンサ容量の関係

脈動抑制制御を適用しても変調率 a や負荷力率  $\cos\theta$ といった入出力条件によっては中性点電圧  $v_{np}$  の脈動を完全には抑制できない。本節では 2.2 で述べた脈動抑制制御を適用した場合において所望の電圧脈動幅  $\Delta v_{np}$  に抑制可能な最小の

コンデンサ容量設計指針について議論する。

定常状態において、 $v_{np}$  の DC 成分は一定値であるが、1 周期内でみると出力周波数の 3 倍で脈動が生じる。中性点電位  $v_{np}$ は(3)式を積分することで求まり、(4)式となる<sup>[4]</sup>。

$$v_{np} = \frac{1}{C} \int i_{np} dt \tag{4}$$

$v_{np}$ が出力周波数 $f_{inv}$ の3倍の周期関数であることに着目すると、 $\Delta v_{np}$ は(4)式の $i_{np}$ の項を絶対値とおき  $1/6f_{inv}$ で定積分をすることで導出できる。(5)式にその結果を記す。ここで $\omega$ は出力角周波数,Cは片側のDCリンクコンデンサである。

$$\Delta v_{np} = \frac{1}{C} \int_0^{1/6 f_{inv}} \left| i_{np} \right| dt \qquad (5)$$

しかし,(5)式中の積分部分は絶対値を含み非線形であるため,代数計算により解を求めることは困難である。そこで,積分部分を無次元化した係数にて表すと,(6)式が得られる $^{[4][8]}$ 。

$$\Delta v_{np} = \frac{\sqrt{2}I_{uv}}{2C\omega} \int_0^{\omega/6} \left| i_{np} / \sqrt{2}I_{uv} \right| d\varphi = \frac{\sqrt{2}I_{uv}}{2C\omega} k_{(a,\cos\theta)} \dots (6)$$

ここで  $I_{uv}$  は線間電流, $\phi$ は出力位相角,そして  $k(a,\cos\theta)$  は電荷係数と定義し,(5)式の積分結果を無次元化して得られる値である。

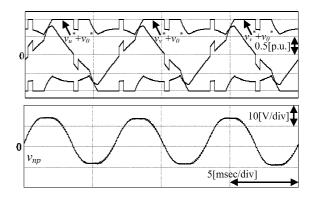

図 3 に電荷係数  $k(a,\cos\theta)$ と変調率 a 及び力率  $\cos\theta$ の関係を示す。変調率は相電圧指令 $(v_u^*)$ の最大値/負荷力率と定義する。電荷係数は変調率及び力率の関数となり、力率が高いほど、変調率が小さいほど、電位変動は小さくなる。

(6)式をキャパシタンスについて解くことで、所望の電圧変動範囲を実現する負荷力率と変調率に応じたコンデンサ最小容量を求めると、(7)式となる。なお、(7)式は表1に記す標準値で規格化して表記している。

$$Y_{pu} = \frac{I_{uv\_pu}}{2\Delta v_{np\_pu}} k_{(a,\cos\theta)} \tag{7}$$

(7)式に  $k(a,\cos\theta)$ を代入するで定常状態の任意の負荷条件に応じて所望の  $\Delta v_{np}$  に抑制可能な DC リンクコンデンサ容量がアドミッタンス  $Y_{pu}$  より求めることができる。

例として、動作点を負荷力率 0.9、変調率 a=1.1、とし、定格電流時の電位変動を 10%以下にできる最小のキャパシタンスを設計する(図 3 中の破線の交点)と、アドミッタンス $Y_{pu}$ は61.3%(= $313\mu$ F@ 10kW, 200Vrms, 50Hz出力時)となる。

#### 〈3·2〉 モータの動作点を考慮した設計法

3.1 章にて変調率 a,力率  $\cos\theta$ ,相電流  $I_u$  そして所望の中性点電圧変動幅  $\Delta v_{np}$  を与えることで必要なコンデンサ最小容量を設計できる方法を示した。ここでは,モータ駆動用途に 3 レベルインバータを適用したことを想定し,トルク T とモータ回転数 N そして  $\Delta v_{np}$  からコンデンサ最小容量を設計する手順を示す。ここでは,一例として,永久磁石モータ (PM モータ)を  $I_d$  = 0 で制御した場合を検討する。

図 4 に PM モータ 1 相分の等価回路とベクトル図を示す。 ここで  $e_u$  は速度起電力, L は電機子巻線の自己インダクタ

Fig. 3. Charge coefficient  $k(a, cos \theta)$ : Relation among charge coefficient and power factor of load and modulation index.

Table.1. Definition of normalized value.

| Normalized value   | Standard value                         |  |

|--------------------|----------------------------------------|--|

| $\Delta v_{np pu}$ | $V_{in}$                               |  |

| $V_{uv\_pu}$       | Line voltage rating: $V_{uv_n}$ [Vrms] |  |

| $I_{uv\_pu}$       | Line current rating: $I_{uv_n}$ [Arms] |  |

| $Y_{pu}$           | $I_{uv n} / V_{uv n}$                  |  |

(a) Equivalent circuit for single phase (b) Phaser vector Fig. 4. The state of PM motor when  $i_d = 0$  control

ンス、Vは相電圧実効値、pは極対数である。図 4 より、(6) 式中と PM モータの各パラメータの関係は(8)から(11)式にて定義できる。ここで $\phi$ 化各相電機子巻線磁束鎖交数で2軸変換後の値を $\phi$ とする。

$$a = \frac{2\sqrt{2}V_u}{V_{in}} \tag{8}$$

$$\omega = \pi p N / 30 \qquad (9)$$

$$T = p \Phi i_q$$

$$\dot{\cdot} I_u = \frac{T}{\sqrt{3} p \Phi} \tag{10}$$

$$\cos \theta = \frac{e_u + RI_u}{\sqrt{(e_u + RI_u)^2 + (\frac{\pi pN}{30} LI_u)^2}} \dots (11)$$

一方,  $e_u$ は(12)式にて定義できるので, (10)式と(12)式を(11)式に代入して, (13)式が得られる。

$$e_u = \left| \frac{d\phi'}{dt} \right| = \frac{\pi p N}{30} \Phi' = \frac{\pi p N}{30} \Phi \dots \tag{12}$$

$$\cos\theta = \frac{\frac{\pi pN}{30}\Phi + \frac{RT}{p\Phi}}{\sqrt{\left(\frac{\pi pN}{30}\Phi + \frac{RT}{p\Phi}\right)^2 + \left(\frac{\pi NLT}{30\Phi}\right)^2}} \quad \dots (13)$$

さらに相電圧実効値  $V_u$ は、(13)式を整理することで求まり(14)式となる。

$$V_{u} = \sqrt{\left(\frac{\pi pN}{30}\boldsymbol{\Phi} + \frac{RT}{p\boldsymbol{\Phi}}\right)^{2} + \left(\frac{\pi NLT}{30\boldsymbol{\Phi}}\right)^{2}} \quad .....(14)$$

(14)式を(8)式に代入することで変調率とモータパラメータの関係が得られ, (15)式となる。

$$a = \frac{2\sqrt{2}}{V_{in}} \sqrt{\left(\frac{\pi pN}{30}\boldsymbol{\Phi} + \frac{RT}{p\boldsymbol{\Phi}}\right)^2 + \left(\frac{\pi NLT}{30\boldsymbol{\Phi}}\right)^2} \quad \dots (15)$$

以上より 3.1 章にて使用したパラメータと  $i_d$  = 0 制御時の PM モータのパラメータの関係式(9)(10)(13)(15)が得られた。

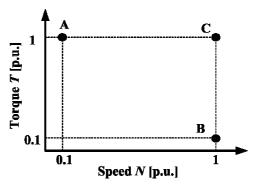

図 5 に速度ートルクカーブ(NT 線図)を示す。A 点は始動時を表しており、B 点は定格電力点、C 点は高速系負荷条件である。以下に各動作点においてひつようとされるコンデンサ容量について検討する。コンデンサ容量は $\Delta v_{np}$  が最大となる条件で設計されるため、そのようなTとNを明らかにする。(6)式から明らかなように $\Delta v_{np}$  は周波数が低いほど、そして電流が大きいほど増加する傾向にある。そこで、低速大トルクとなるA点、高速低トルクとなるB点、そして高速大トルクとなるC点のいずれかで $\Delta v_{np}$  が最大となる可能性が高い。

これらの式を用いて表 2 に記すモータパラメータを使用した場合に  $V_{in}$ =220V, $f_{inv}$ =10kHz で  $\Delta v_{np}$ を 10%以下に抑制可能なコンデンサ最小容量の設計を行う。ABC 点における出力周波数の 3 倍での電圧脈動幅  $\Delta v_{np}$ は(6)式より求まり,0V@A点(a=0.140,  $\cos\theta$ =0.995),0V @B点(a=1.03,  $\cos\theta$ =1.00),1.39V@C点(a=1.07,  $\cos\theta$ =0.992) となる。したがって,誘導機に比べて PM モータは力率を高く維持できることから変調率が高くても電圧脈動を良く抑制でき,3 レベルインバータを適用しやすいといえる。また,以上の検討より,PM モータ駆動においてはコンデンサを設計する際は,C点(最高速の軽負荷領域)にて設計すればよいことがわかる。ただし, $\Delta v_{np}$ の定義は出力周波数の 3 倍での電圧脈動のみを表し,スイッチングリプルは考慮していない。スイッチングリプルの最大値  $\max[\Delta v_{np,sw}]$ は(16)式にて定義できる。

$$\max[\Delta v_{np\_sw}] = \frac{\sqrt{2}I_u}{Cf_{inv}} \tag{16}$$

(6)式と(16)式の和が中性点電圧変動幅となることから,所望の中性点電圧変動幅に抑制可能なコンデンサ容量 C は

Table.2. PM motor parameters for design example.

| Rating output $P_r$               | 800 W         |

|-----------------------------------|---------------|

| Rating speed $N_r$                | 2000 rpm      |

| Armature resistance $R$           | $0.425\Omega$ |

| Armature Self-inductance $L$      | 0.00378H      |

| Armature Flux linkage $\Phi$      | 0.233 V·s/rad |

| Armature pairs of poles p         | 2             |

| Rating Torque $T_r$               | 3.82N⋅m       |

| Rating armature current of q axis | 8.20A         |

Fig.5. Speed torque curve for capacitor design.

Table.3. Simulation condition.

| Input voltage $V_{in}$       | 200[V]  |

|------------------------------|---------|

| Output power P               | 1.0[kW] |

| Output frequency $f_{inv}$   | 50[Hz]  |

| Switching frequency $f_{sw}$ | 10[kHz] |

| DC link capacitance C        | 100[μF] |

| Load                         | R-L     |

(17)式にて求まる。

$$C = \frac{\sqrt{2}I_{uv}(k_{(a,\cos\theta)} + 4\pi)}{2\omega(\Delta v_{nn} + \Delta v_{nn-sw})} \dots (17)$$

(17)式より、コンデンサ容量は 16.1µF となる。

#### 4. シミュレーション及び実験結果

3 章で記したコンデンサ容量設計指針の検証を行うために 1kW 負荷の実機を試作した。表 3 に試作機の仕様を示す。

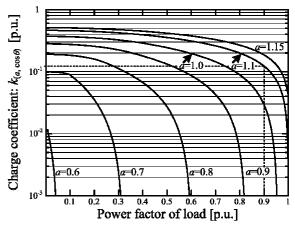

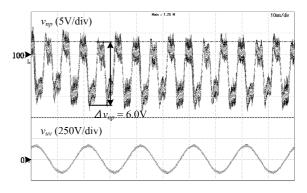

図 6 の各波形は上から中性点電圧  $v_{np}$ , u 相電圧  $v_u$ , u 相電流  $i_u$  である。ただし, $v_u$  と  $v_{np}$  に関してはカットオフ周波数 1kHz のローパスフィルター(LPF)通過後の波形である。変調率 a は 1.0 で相抵抗は 11.5  $\Omega$  に固定した上で負荷インダクタンスを調節し  $\cos \theta$  を 0.847 とした。図 6(a) よりこの条件では中性点電圧は 30 V 程度で脈動している。この電圧脈動を抑制するために 2.2 章に記した脈動抑制制御を試作機に適用する。図 6(b)にその結果を示す。中性点電圧の脈動は 6 V 程度に抑制されている事を確認できる。

本試作機を用いて 3.1 章に示した DC リンクコンデンサ容量設計指針の実機検証を行う。コンデンサ容量は所望の中性点電圧変動幅  $\Delta v_{np}$  を(7)式に代入することで求まるが,ここではコンデンサ容量を一定値とし,その代わりに変数と

(b) With suppression control Fig.6. Result of suppression control.(a:1.0,  $\cos\theta$ . 0.847).

なる $\Delta v_{np}$ を評価することで、(7)式の妥当性を検証する。

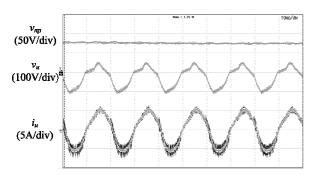

図 7 に負荷力率 0.855 で変調率 1.0 の条件で測定した波形を記す。それぞれの波形は 1 k Hz のローパスフィルターを通過した後の波形であり,上から中性点電圧,u-v 線間電圧である。図 7(a)はシミュレーション波形で(b)は実験波形である。実験波形は波形に乱れが生じているが,これはシミュレーションには考慮されていない電流検出誤差やデッドタイム等の影響によるものである。図 7(a)と(b)に示されている  $\Delta v_{np}$  は出力周波数の 3 倍で脈動する中性点電圧変動幅であり,この値を測定し計算結果と比較を行う。

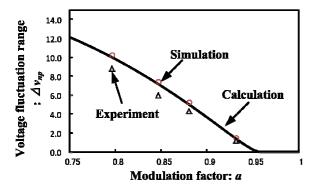

図 8 に力率の変化に応じた  $\Delta v_{np}$  の推移を示す。ここでは,変調率は 1.0 に固定し,負荷インダクタンスのみを変化させ力率を変えている。実線は(6)式より求めた計算結果で,三角印はシミュレーション結果,丸印は実験結果を表す。シミュレーションと計算の結果はよく一致しているが実験結果については差が見られる。これは,計算やシミュレーションでは考慮されていない,デッドタイムや電流検出誤差等が影響しているものと考えられる。

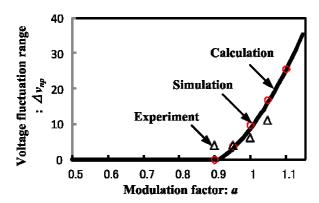

同様にして、図 9 に変調率の変化に応じた  $\Delta v_{np}$  の推移を示す。ここでは、力率は 0.85 に固定されている。計算結果によると変調率 0.92 以下では  $\Delta v_{np}$  を完全に抑制でき、それ以上では  $\Delta v_{np}$  が増加し、変調率 1.15 では 36 V 程度に達する。計算結果とシミュレーション結果はよく一致している。しかし実験結果については 2 種類の差が見られる。変調率 1.0 以上では差が生じており、この原因としては前述と同じ事が考えられる。変調率が 0.95 以下では計算結果では電圧脈動が完全に抑制されるはずにも関わらず、実験結果では脈動が発生している。

(b) Experimental waveforms

Fig. 7. The waveforms of neutral point voltage and output voltage when the modulation index a is 1.0 and Power factor  $\cos \theta$  is 0.855.

図10に本現象を詳しく知るために変調率0.80における実験波形を示す。インバータの出力電流が歪んでいるが、これは中性点電位が平均的に負に偏っていることに起因する。実験結果では本来中性点電圧の平均値は100Vに設定しているが、マイナス側に偏っている。これは、本稿で取り上げる脈動抑制制御では中性点電圧の検出を用いないため定常的な電圧偏差に対しては効果がないためである。定常的なアンバランスは例えば文献[10][11]に詳細されている方法を導入することにより解消できると考えられる。

#### 5. まとめ

3 レベルインバータは中性点電圧が脈動する問題があるため、これまでに種々の中性点電圧制御法が提案されている。しかしながら、いずれの方式も変調率や力率の値によっては電圧変動を完全には抑制できず、更なる電圧脈動の抑制の為にはコンデンサ容量を大きく設計する必要がある。不必要なコストや回路体積の増加を避けるためには最小のコンデンサ容量設計法が必要である。本稿ではキャリア比較変調に適用可能な中性点電圧の脈動抑制制御を適用した場合におけるコンデンサ最小容量設計法について議論

Fig. 8. Relationship between power factor and the voltage fluctuation of neutral point with simulation results.

Fig. 9. Relationship between modulation factor and the voltage fluctuation of neutral point with simulation results.

Fig.10. Simulation result (Modulation index a:0.8, Power factor  $\cos \theta$ . 0.847).

した。

まず、定常状態における入出力条件とコンデンサ容量の関係を明らかにした。次に、1kW 負荷の実機を試作し、この関係が実験結果とよく一致することを確認した。この関係に基づいて、PM モータに id = 0 制御を適用した場合において、トルクと回転数そして所望の中性点電圧変動幅を与えることで最小のコンデンサ容量を設計できる方法を示した。実際のモータパラメータを用いて計算した結果、負荷力率が 0.99 以上であり、中性点電圧脈動を十分に抑制可

能であることが示された。

今後は提案した設計法をモータの加速時などの過渡状態 にまで拡張し、モータを負荷とした実機による検証を行う。

#### 文 献

- Akira Nabae, Isao Takahashi, Hirofumi Akagi: "A New Neutral-Point-Clamped PWM Inverter", IEEE Trans., Vol.IA-17, No.5 pp.518-523 (1981)

- (2) 江口直也, 藤平龍彦: "パワーエレクトロニクスとパワー半導体の シナジーによる技術の強化", 富士時報, Vol.83, No.1 pp.14-18 (2010)

- (3) 中沢洋介, 内藤治夫: "NPC インバータのパルス幅制限による波形 ひずみをなくす PWM 方式と中性点電位制御", 電学論 D, Vol.116, No.4 pp.412-419 (1996)

- (4) 小笠原悟司,小沢直,赤木泰文:「中性点クランプ形 PWM インバータの中性点電位変動の解析」,電学論 D, Vol.113, No.1 pp.41-48 (1993)

- (5) 川畑隆夫,小山正人,玉井伸三,藤井俊行,打田良平:「GTOの最小パルス幅の影響と中性点電圧制御を考慮した3レベルインバータの変調法」、電学論D, Vol.113, No.7 pp.865-873 (1993)

- (6) 上園恵一, 霍斌, 宮下一郎: 「3 レベルインバータの制御方法」, 東洋電機技報, Vol.巻数, No.90 pp.2-8 (1995)

- (7) 霍斌,宮下一郎,曽根悟:「3 レベルインバータの中性点電位変動を 抑制した空間ベクトル PWM 波形生成法」,電学論 D, Vol.116, No.1 pp.42-49 (1996)

- (8) 田中孝明, 伊東淳一:「中性点クランプ形3 レベルインバータのコンデンサ容量設計指針」,第20回電気学会東京支部新潟支所研究発表会予稿集,IV-02 p.18 (2010)

- (9) Rangarajan M. Tallam, Rajendra Naik, Thomas A. Nondahl: "A Carrier-based PWM Scheme for Neutral-Point Voltage Balancing in Three-Level Inverters", IEEE Trans., Vol.41, No.6 pp.1734-1743 (2005)

- (10) 福田昭治,松本泰雅,佐川哲:「中性点クランプ形 PWM コンバータのモデリングと最適レギュレータを用いた中性点電位制御」,電学論D, Vol.119, No.1 pp.109-196 (1999)

- (11) 神谷茂, 鈴木研, 大沢博, 橋井眞: 「3 レベルインバータ中性点電流 の直流分の解析と中性点電位の抑制制御法」, 電気学会全国大会, 516, pp.561-562 (1993)