# 太陽光発電系統連系用インバータにおけるマルチレベル変換器 トポロジーの性能比較

樫原 有吾\* 伊東 淳一(長岡技術科学大学)

The comparison of the efficiency and power density of the multilevel converter topologies for PV inverter Yugo Kashihara\*, Jun-ichi Itoh, (Nagaoka University of Technology)

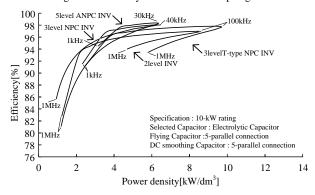

Abstract:- This paper discusses the performance of a 5-level ANPC inverter for PV system which is calculated by using the optimization designing method for a 5-level ANPC inverter. In addition, the performance of a 5-level ANPC inverter for PV system is compared with the conventional 2-level inverter and 3-level NPC inverter and 3-level T-type NPC inverter. The point of the performance comparison of the four converters for PV system is that 5-level ANPC inverter and 3-level NPC inverter can achieve high efficiency and high power density at switching frequency from 1 kHz to 1 MHz. The 5-level ANPC inverter can achieve high efficiency converter. On other hand, the 3-level T-type NPC inverter can achieve high power density converter.

**キーワード**:太陽光発電,インバータ,マルチレベル変換器,アクティブ中性点クランプ,インバータ損失 (PV, Inverter, multilevel converter, Active Neutral-Point-Clamped, Inverter loss)

# 1. はじめに

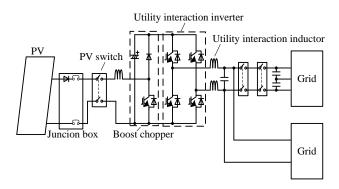

近年、太陽光などの新エネルギーシステムを用いた系統連系システムが盛んに研究されている(3)。Fig.1 のような系統連系システムに求められる要求として、低高調波、高力率、連系リアクトルの小型化などが挙げられる。一方で、電力変換器の出力電圧の高調波低減、電流応答の高速化の観点から、マルチレベル電力変換器が研究されている(1)-(5)。マルチレベル電力変換器は従来の 2 レベルの電力変換器と比較すると、①レベル数 n に対しスイッチング素子の耐圧をn-1分の1に低減できること、②複数レベルの電圧を出力するので出力電圧の高調波を低減できる、③1 パルス当たりの電圧変動が小さいのでリプル電流が小さくリアクトルの体積が低減できることが利点としてあげられる。これらのマルチレベル変換器の利点は、系統連系システムの要求を満たしており、系統連系システムに適している。

代表的なマルチレベル変換器の回路構成として、中性点クランプ(以下 NPC)方式と、フライングキャパシタ(以下 FC)方式があげられる<sup>(1)(4)</sup>。NPC 方式は、ダイオードによって中性点電圧をクランプすることで複数の電圧レベルを出力する。しかし、出力レベルに応じてスイッチング素子が増加するため、各スイッチング素子の損失増加が懸念される。FC 方式は、直流リンクコンデンサと FC 電圧を合成することで複数の電圧レベルを出力する。しかし、レベル数の増加に伴い、コンデンサが多数必要となり、各コンデンサの

電圧バランス制御が困難になる。

そこで筆者らは、マルチレベル電力変換器の一方式として、5レベルアクティブ中性点クランプ形(以下 ANPC)インバータに注目している<sup>(2)(3)</sup>。ANPC 方式は、NPC 方式と FC 方式を組み合わせた回路構成となっており、従来方式と比較すると、通過素子数が少なく、従来方式の短所を解決でき、低コスト化、高効率化が期待できる。

これまでに、筆者らは数式を用いた 5 レベル ANPC インバータの最適設計法について検討を行ってきた(4)。数式を用いた理論解析の場合、デバイスパラメータや回路パラメータに応じて、容易に損失が求められるため、最適化の検討がしやすくなるからである。そのため、体積の検討や高効率・高パワー密度等の要求を満たす変換器の設計を容易に行なうことができる。

本論文では、これまで検討した数式を用いた 5 レベル ANPC インバータの最適設計法を太陽光発電用系統連系システムに適用する。さらに、従来回路である 2 レベルインバータや 3 レベル NPC インバータ, 3 レベル T-type NPC インバータについても数式を用いた設計を行い、パレートフロントを用いて各変換器の性能を比較する。本稿では、まず、PV 用系統連系システムに適用する変換器と設計手順について説明する。次に、各変換器のパラメータ設計について説明する。最後に、パラメータ設計法を用いて PV システム用系統連系インバータを設計し、パレートフロントによる変換器性能について検討する。その結果、5 レベル ANPC

インバータが最も高効率な変換器であること、また、3 レベル T-type NPC インバータが最も高パワー密度な変換器であることがわかったので報告する。

## 2. 回路トポロジーおよび変換器の設計手順

# 〈2·1〉回路トポロジー

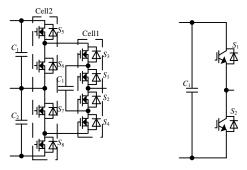

Fig.2 に検討するインバータトポロジー図を示す。本論文では、5 レベル ANPC トポロジー、2 レベルトポロジー、3 レベル NPC トポロジー、3 レベル T-type NPC トポロジーの4 つの変換器について検討する。

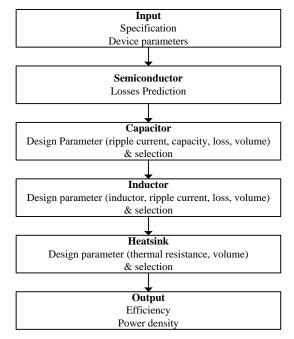

#### 〈2·2〉変換器設計手順

Fig.3 に変換器の設計フローチャートを示す。Fig.3 の設計チャートは、変換器の仕様やデバイスパラメータを入力とする。これらのパラメータを用いて、半導体素子、キャパシタ、インダクタ、ヒートシンクのパラメータを導出する。個々のパラメータから変換器全体の効率とパワー密度を導出する。まず、数式による検討では、製品のパラメータから変換器性能を評価する。そのため、実際の半導体素子の損失が容易に検討することができる。

キャパシタの設計部分では、容量、リプル電流、損失、体積の 4 つのパラメータについて検討を行なう。特に、キャパシタの体積は変換器の高パワー密度化に対する重要な要素となる。キャパシタの体積は製品から体積係数を導出して計算する。

リアクトルの設計部分では、インダクタ、リプル電流、 損失、体積の 4 つのパラメータについて検討を行なう。特 に、インダクタの体積は変換器の小型化に対して重要な要 素である。インダクタの体積は、Area Product を用いて設計 を行なう<sup>(5)</sup>。

ヒートシンクの設計では、熱抵抗と体積のパラメータについて検討を行なう。ヒートシンクの体積の見積もりは、CSPIを用いて検討を行なう。CSPIは、単位体積当たりの熱抵抗の逆数で、この数値が大きいほど単位体積当たりの冷却能力が大きいことを示す。

## 3. マルチレベル変換器への適用

2 章で述べた変換器の設計チャートを用いてマルチレベルインバータの設計を行なう。

## 〈3・1〉半導体素子の損失計算法

本節では半導体の損失計算について説明する。電力損失は以下の条件で計算を行う。

1)負荷電流リプルは無視できる(電流源負荷とみなせる) 2)キャパシタのリプル電圧は無視できる(直流電圧源とみ

#### 3.1.15 レベル ANPC トポロジー

なせる)

本節では、5 レベル ANPC インバータの損失計算方法について説明する<sup>(4)</sup>。Fig.2(a)の回路図において、Cell1 と Cell2 でスイッチング動作が異なるため、Cell ごとに損失計算の検討を行なう。また、導通損失はスイッチ(IGBT、MOSFET) 側と環流ダイオード(FWD)側に発生する損失に分けること

Fig.1. A PV system.

(a) Five-level ANPC inverter. (b) Two-level inverter.

(c)Three-level NPC inverter.(d) Three-level T-type NPC inverter.

Fig.2. Single leg multilevel converter topologies.

Fig.3. Single phase 5-level ANPC inverter circuit topology.

ができる。ここで、素子に流れる正の電流はすべてスイッチ側に、負の電流は FWD 側を流れると仮定する。また、MOSFET の場合、オン抵抗が小さければスイッチ側に正負両方向に電流が流れる。しかし、FWD のオン電圧特性をMOSFET と同一に設定することで損失は計算できる。

Cell1 の素子 1 つに発生する順方向の導通損失  $P_{5A\_con\_Cell1\_sw}$  は(1)式にて得られる。一方、FWD 側の損失  $P_{5A\_con\_Cell1\_FWD}$  は(2)式で導出することができる。

$$P_{5A\_com\_Cell \, 1\_mv} = I_m \left( \frac{v_0}{2\pi} - \frac{1}{2} v_0 \cos \phi + \frac{1}{8\pi} I_m r_{on} \sin 2\phi - \frac{1}{4\pi} I_m r_{on} \phi - \frac{2}{3\pi} I_m a r_{on} \cos \phi - \frac{1}{4} a v_0 \cos \phi \right) \qquad \dots \dots (1)$$

$$P_{SA\_com\_Cell\,1\_FWD} = I_m \left( \frac{v_0}{2\pi} + \frac{1}{2} v_0 \cos \phi + \frac{1}{8\pi} I_m r_{on} \sin 2\phi + \frac{1}{4\pi} I_m r_{on} + \frac{1}{4\pi} I_m r_{on} \phi - \frac{2}{3\pi} I_m a r_{on} \cos \phi - \frac{1}{4} a v_0 \cos \phi \right)$$

.....(2)

ここで、a は指令値の振幅、 $r_{on}$  はスイッチのオン抵抗、 $v_0$  は 0A の時のオン電圧降下、 $I_m$  は負荷電流ピーク値、 $\phi$ は負荷力率である。また、オン電圧は IGBT を想定し、PN 接合による電圧降下と抵抗分にある電圧降下として表現しているが、MOSFET は抵抗特性であるため、(1)式及び(2)式において  $v_0$ =0 とすれば表現できる。

Cell2 の導通損失について述べる。Cell2 素子の中で、 $S_5$ 、 $S_7$  は出力電圧指令値が正の時にオン、 $S_6$ 、 $S_8$  は出力電圧指令値が負の時にオンするため、スイッチ電流が異なる。 $S_5$ 、 $S_7$ のスイッチ側の導通損失  $P_{5A\_con\_Cell2\_SWA}$  は(3)式のように得られる。また、 $S_5$ 、 $S_7$ の FWD 側の導通損失  $P_{5A\_con\_Cell2\_FWDA}$  は(4)式で導出することができる。

$$P_{SA\_com\_Cell\ 2\_FWDA} = \frac{1}{12\pi} \left[ I_m a \left( 8I_m r_{om} \sin \left( \frac{\phi}{2} \right)^4 - 3v_0 \sin \phi + 3\phi v_0 \cos \phi \right) \right] (4)$$

同様に、 $S_6$ 、 $S_8$ のスイッチ側の導通損失  $P_{5A\_con\_Cell2\_swB}$  と FWD 側の導通損失  $P_{5A\_con\_Cell2\_FWDB}$  は、(5)、(6)式で得られる。

$$P_{SA\_com\_Cell \ 2\_mB} = \frac{1}{2\pi} \left[ I_m v_0 (\cos \phi + 1) + I_m^2 r \left( \frac{\pi}{2} + \frac{\phi}{2} - \frac{1}{4} \sin 2\phi \right) - I_m a v_0 \left( \frac{\pi}{2} \cos \phi - \frac{1}{2} \sin \phi + \frac{1}{2} \phi \cos \phi \right) \right]$$

$$+ I_m a r \left( \frac{1}{6} \cos 2\phi + \frac{2}{3} \cos \phi + \frac{1}{2} \right)$$

(5)

$$P_{5A_{-com_{-}Cell\ 2_{-}FWDB}} = \frac{1}{2\pi} \left[ I_{m}^{2} r \left( \frac{\phi}{2} - \frac{1}{4} \sin 2\phi \right) - I_{m} v_{0} + I_{m} v_{0} \cos \phi \right. \\ \left. - \frac{1}{2} I_{m} a v_{0} \left( \sin \phi - \phi \cos \phi \right) + I_{m}^{2} a r \left( \frac{1}{6} \cos 2\phi - \frac{2}{3} \cos \phi + \frac{1}{2} \right) \right] \dots (6)$$

スイッチング損失はスイッチに印加される電圧とスイッチに流れる電流に比例すると仮定する。このとき、Cell1のスイッチング損失 $P_{SA\_sw\_Cell1}$ はデューティ比によらず、流れ

る電流とスイッチング回数に依存するので, (7)式で導出することができる。

$$P_{5A_{-m}e_{-}Cell\ 1} = \frac{1}{(n-1)\pi} \frac{E_{dc} I_{m}}{E_{dcd} I_{md}} (e_{cm} + e_{eff}) f_{c}$$

(7)

ここで、n は出力電圧レベル、 $E_{dc}$  は入力電圧、 $e_{on}$  はスイッチング 1 回のターンオン損失(J)、 $e_{on}$  はデータシートにあるターンオン損失(J)、 $e_{of}$  はデータシートにあるターンオフ損失(J)、 $E_{dcd}$  及び  $I_{md}$  はデータシート上のターンオン損失、ターンオフ損失の測定条件時の電圧と電流である。

また、FWD のリカバリ損失  $P_{5A\_rec\_Cell1}$  も(7)式と同様に (8) 式で導出することができる。

$$P_{SA_{-mc_{-}}Cell1} = \frac{1}{(n-1)\pi} \frac{E_{dc}I_{m}}{E_{dcd}I_{md}} e_{m} f_{c}$$

(8)

ここで、 $e_r$ はリカバリ損失(J)である。

Cell2 のスイッチング損失は、Cell2 のスイッチが出力周波数でスイッチングを行うため、キャリア周波数と同じ周波数でスイッチングする Cell1 のスイッチング損失と比較して、Cell2 のスイッチング損失は十分小さく無視できる。

#### 3.1.22 レベルトポロジー

本節では、2 レベルインバータの損失計算方法について説明する。Fig.2(b)において、半導体素子 1 つに発生する順方向の導通損失  $P_{2l\_con\_sw}$  は(9)式にて得られる。一方、FWD 側の損失  $P_{2l\_con\_FWD}$  は(10)式で導出することができる。

$$P_{2I_{-com_{-}mr}} = \left(\frac{1}{2\pi}v_{0} + \frac{1}{8}I_{m}r_{s}\right)I_{m} + \left(\frac{1}{3\pi}ar_{s}I_{m} + \frac{1}{8}av_{0}\right)I_{m}\cos\phi \dots (9)$$

$$P_{2I_{-con_{-}FWD}} = \left(\frac{1}{2\pi}v_{0} + \frac{1}{8}I_{m}r_{s}\right)I_{m} - \left(\frac{1}{3\pi}ar_{s}I_{m} - \frac{1}{8}av_{0}\right)I_{m}\cos\phi \dots (10)$$

スイッチング損失は(7)式, リカバリ損失は(8)式で導出することができる。

# 3.1.3 3 レベル NPC トポロジー

本節では、3 レベル NPC インバータの損失計算方法について説明する。Fig.2(c)において、上下アームに発生する損失は同じである。しかし、アーム中の各素子に流れる電流が異なるため、それぞれに発生する損失は異なる。 $S_1$  と  $S_4$  の素子に発生する順方向の導通損失  $P_{3N\_con\_S1\_sw}$  は(11)式にて得られる。一方、FWD 側の損失  $P_{3N\_con\_S1\_FWD}$  は(12)式で導出することができる。

$$P_{3N_{-}\cos_{-}s1_{-}mr} = \frac{aI_{m}}{2\pi} \left\{ rI_{m} \left[ \frac{1}{6}\cos(2\phi) + \frac{2}{3}\cos(\phi) + \frac{1}{2} \right] + v_{0} \left[ \frac{\pi}{2}\cos\phi - \frac{1}{2}\sin\phi + \frac{\phi}{2}\cos\phi \right] \right\}$$

(11)

$$P_{3N_{-\cos{-}}S1_{-}FWD} = \frac{aI_{m}}{2\pi} \left\{ rI_{m} \frac{1}{3} \left[ 4\sin^{2}\left(\frac{\phi}{2}\right) - \sin^{2}\phi \right] - \frac{v_{0}}{2} \left[ \sin\phi - \phi\cos\phi \right] \right\}$$

(12)

$S_2$ と  $S_3$ の素子に発生する順方向の導通損失  $P_{3N\_con\_S2\_sw}$ と FWD 側の損失  $P_{3N\_con\_S2\_FWD}$  は(13), (14)式で導出できる。

$$P_{3N_{-}\cos_{-}S^{2}_{-}m^{2}} = \frac{I_{m}}{2\pi} \left\{ rI_{m} \left[ \frac{\pi}{2} + \frac{\phi}{2} - \frac{1}{4}\sin 2\phi \right] + v_{0} \left[\cos \phi + 1\right] \right\}$$

$$+ \frac{1}{2\pi} I_{m} \left[ rI_{m} \left[ \left( \frac{1}{4}\sin 2\phi - \frac{\phi}{2} \right) + a \left( \frac{1}{3}\sin^{2}\phi - \frac{4}{3}\sin^{2}\left(\frac{\phi}{2}\right) \right) \right] \dots (13)$$

$$+ v_{0} \left[ (1 - \cos\phi) + a \left( \frac{1}{2}\sin\phi - \frac{\phi}{2}\cos\phi \right) \right] \right\}$$

$$P_{3N_{-\cos_{-}}S^{2}_{-}FWD} = \frac{aI_{m}}{2\pi} \left\{ rI_{m} \frac{1}{3} \left[ 4 \sin^{2} \left( \frac{\phi}{2} \right) - \sin^{2} \phi \right] - \frac{v_{0}}{2} \left[ \sin \phi - \phi \cos \phi \right] \right\}$$

(14)

$D_1$ と  $D_2$ の素子に発生する導通損失  $P_{3N\_con\_D}$ は(15)式にて得られる。

$$\begin{split} P_{3N_{-}\cos m_{-}D} &= \frac{1}{2\pi} I_{m} \left\{ r I_{m} \left[ \left( \frac{\pi}{2} + \frac{\phi}{2} - \frac{1}{4} \sin 2\phi \right) - a \left( \frac{1}{6} \cos 2\phi + \frac{2}{3} \cos \phi + \frac{1}{2} \right) \right] \right. \\ &+ v_{0} \left[ (\cos \phi + 1) - a \left( \frac{\pi}{2} \cos \phi - \frac{1}{2} \sin \phi + \frac{\phi}{2} \cos \phi \right) \right] \right\} \\ &+ \frac{1}{2\pi} I_{m} \left\{ r I_{m} \left[ \left( \frac{1}{4} \sin 2\phi - \frac{\phi}{2} \right) + a \left( \frac{1}{3} \sin^{2} \phi - \frac{4}{3} \sin^{2} \left( \frac{\phi}{2} \right) \right) \right] \right. \\ &+ v_{0} \left[ (1 - \cos \phi) + a \left( \frac{1}{2} \sin \phi - \frac{\phi}{2} \cos \phi \right) \right] \right\} \end{split}$$

3 レベル NPC インバータのスイッチング損失  $P_{3N\_sw}$ は(16) 式で, リカバリ損失  $P_{3N\_rec}$ は(17)で導出できる。

$$P_{3N_{-NW}} = \frac{1}{(n-1)\pi} \frac{E_{dc} I_{m}}{E_{dcd} I_{md}} (e_{cn} + e_{eff}) \frac{f_{c}}{2}$$

(16)

$$P_{3N_{-mc}} = \frac{1}{(n-1)\pi} \frac{E_{dc}I_{m}}{E_{dc}I_{md}} e_{\pi} \frac{f_{c}}{2}$$

(17)

#### 3.1.43 レベル T-type NPC トポロジー

本節では、3 レベル NPC インバータの損失計算方法について説明する。Fig.2(d)において、3 レベル T-type NPC インバータのスイッチング素子の動作は、3 レベル NPC インバータのスイッチング動作と同じである。そのため、3 レベル T-type NPC インバータの  $S_1$  及び  $S_2$  の導通損失は、(11)式及び(12)式で導出できる。また、スイッチング損失  $P_{3TN\_swl}$  及びリカバリ損失  $P_{3TN\_swl}$  は(18)式、(19)式で導出できる。

$$P_{3TN_{-}^{mv1}} = \frac{2}{(n-1)\pi} \frac{E_{dc} I_{m}}{E_{dcd} I_{md}} \left( e_{on} + e_{off} \right) \frac{f_{c}}{2} ....$$

(18)

$$P_{3TN_{-}nc1} = \frac{2}{(n-1)\pi} \frac{E_{dc} I_{m}}{E_{dcd} I_{md}} e_{\pi} \frac{f_{c}}{2} \dots (19)$$

一方で、3 レベル T-type NPC インバータの  $S_3$  及び  $S_4$  の導通損失は(15)式で導出することができる。また、スイッチング損失  $P_{3TN\_rec3}$  及びリカバリ損失  $P_{3TN\_rec3}$  は(20)式、(21)式で導出できる。

$$P_{3N_{-}m^{2}3} = \frac{2}{(n-1)\pi} \frac{E_{\pm}I_{m}}{E_{\pm}d_{eff}I_{mf}} (e_{on} + e_{off}) f_{c} \qquad (20)$$

$$P_{3N_{-}mc3} = \frac{2}{(n-1)\pi} \frac{E_{\pm l_m}}{E_{\pm J_{-}l_m}} e_n f_c \qquad (21)$$

# 3.1.5 実験による理論式の妥当性の検討

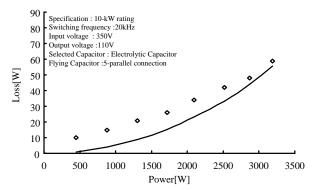

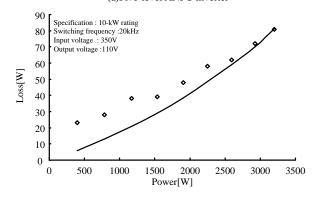

Fig.4 に 3.3kW 定格の単相ハーフブリッジの 5 レベル ANPC インバータと 3 レベル NPC インバータを設計し、パワーメータ(WT1600:YOKOGAWA)を用いて測定した損失と各変換器の損失計算式を用いて推定した損失を比較した結果を示す。3.3kW 定格運電時の理論損失と実機の損失の誤差率は 5 レベル ANPC インバータが 6%,3 レベル NPC インバータが 1%となり、理論式の妥当性を確認した。軽負荷時に一致しなくなる原因の 1 つとして、スイッチング素子の浮

遊容量に電荷が充電され、放電するときにスイッチング素子のオン抵抗に流れ、このときに発生する損失が軽負荷時における誤差として出ていることがあげられる。

#### 〈3·2〉キャパシタの設計

本節ではキャパシタのパラメータ設計法について述べる<sup>(4)</sup>。

#### 3.2.1 キャパシタの容量設計

5 レベル ANPC インバータのフライングキャパシタの容量  $C_{FC}$  はキャパシタに流れる電流,リプル電圧,フライングキャパシタ電圧の充電もしくは放電時間の時間積から導出することができ,(22)式で導出できる。

$$C_{FC} = \frac{I_m T}{8\Delta V_{ros}} \frac{E_{dc}}{V} \tag{22}$$

ここで、 $\Delta V_{FC}$ はリプル電圧, $I_m$ は負荷電流ピーク値,Tはキャリア周期, $E_{dc}$ は直流電圧, $V_m$ は出力電圧最大値である。一方で,5レベル ANPC インバータの直流平滑キャパシタの容量  $C_{FC}$ は,マルチレベル電圧の出力に直流中点電位を使用するため,直流平滑キャパシタ  $C_2$ ,  $C_3$  を直列に接続する。直流平滑キャパシタ容量  $C_{DCSC}$ は,中点電位の変動をもとに設計し,((23)式となる。

$$C_{DCSC} = \frac{V_m}{2\omega\Delta V_m E_{DC}} I_m \left(\sqrt{3} - \frac{\pi}{3}\right) \dots (23)$$

ここで、 $\Delta V_{cn}$  は直流平滑キャパシタの最大電圧リプルである。また、3 レベル NPC インバータ及び 3 レベル T-type NPC インバータの直流平滑キャパシタも(23)式で同様に設計することができる。

(a)Five-level ANPC inverter

(b)Three-level NPC inverter

Fig.4. Losses of multilevel converters.

また、単相の場合は(24)式のように得られる。

$$C_{DCC} = \frac{V_m}{2\omega\Delta v_{\perp} E_{\perp}} I_m \pi \qquad (24)$$

#### 3.2.2 キャパシタの損失計算法

キャパシタの損失  $P_{Cap}$ は、等価直列抵抗(以下 ESR)で発生する。 $P_{Cap}$ はキャパシタに流れる電流より(25)式で計算できる $^{(6)}$ 。

$$P_{Cop} = I_{mx_{-}Cop}^{2} R_{ESR} \qquad (25)$$

ここで、 $I_{rms\_Cap}$  はキャパシタに流れるリプル電流の実効値、 $R_{ESR}$  はキャパシタの ESR である。キャパシタの電流は、負荷力率と変調率の関数となる。これらは無次元であるから、電流実効値係数  $K_c$  を導入し、(26)式にて、電流実効値を求める。電流実効値係数  $K_c$  は正規化したシミュレーションにより、リプル電流実効値、負荷力率と変調率の関係を求める<sup>(4)</sup>。

$$I_{ms\_Cap} = K_c I_m \qquad (26)$$

## 3.2.3 キャパシタの体積計算法

本節ではキャパシタの体積計算法について説明する。キャパシタの体積は、メーカの製品シリーズから行う<sup>(7)</sup>。

#### 1)フィルムコンデンサ

フィルムコンデンサの体積はエネルギー密度に比例し(27)式で導出することができる。

$$V_{CF} = \gamma_{V_{CF}}^{-1} \frac{1}{2} C_F U_o^2 \qquad (27)$$

ここで $\gamma^{-1}_{VCF}$ はフィルムコンデンサの体積係数,  $C_F$ はコンデンサの容量,  $U_O$ はコンデンサの印加電圧である。

#### 2)電解コンデンサ

電解コンデンサの体積は、電解コンデンサのリプル電流 実行値に比例し、(28)式で表すことができる。

$$V_{CE} = \gamma_{V_{CE}}^{-1} I_{C,RMS}$$

(28)

ここで、 $V_{CE}$  はコンデンサの体積、 $\gamma^1_{VCE}$  は電解コンデンサの体積係数、 $I_{C,RMS}$  は電解コンデンサに流れる電流リプル実効値である。

# 〈3·3〉リアクトルの設計

本節では系統連系インダクタについて説明する $^{(6)}$ 。マルチレベルインバータの連系インダクタ  $L_M$ は(29)式で, 2 レベルインバータの連系インダクタ  $L_{2L}$ は(30)式となる。

$$L_{M} = \frac{V_{dc} - \sqrt{3}V_{m}}{(n-1)\Delta I} \left(\sqrt{3} \frac{V_{m}}{E_{dc}} - \frac{1}{2}\right) T \qquad (29)$$

$$L_{2L} = \frac{V_m}{2\Delta I} \left( 1 - \frac{V_m}{E_{dc}} \right) T \qquad (30)$$

また,系統連系インダクタの体積は,Area Product $^{(5)}$ を用いて検討を行い, $^{(31)}$ 式で決定できる。

$$V_{L} = K_{v} \left( \frac{2W}{K_{u}B_{m}J_{w}} \right)^{\frac{3}{4}} \dots (31)$$

ここで、 $K_V$ はコアの形状から決定される定数、Wはリアクトルに蓄積されるエネルギー、 $K_u$ は窓の線積率、 $B_m$ はコアの最大磁束密度、 $J_w$ は巻き線の電流密度である。

#### 〈3・4〉放熱フィンの設計

放熱フィンは、CSPI を用いて検討する<sup>(7)</sup>。CSPI は(32)式で表される。

$$CSPI = \frac{1}{R_{th}V_0} \tag{32}$$

ここで、 $R_h$ はフィンの熱抵抗、 $V_0$ はフィンの体積である。 また、フィンの熱抵抗は(33)式で得られる。

$$R_{th(f-a)} = \frac{T_j - T_a}{P_j} - R_{th(f-s)}$$

(33)

ここで、 $T_j$  はスイッチ素子のジャンクション温度、 $T_a$  は周囲温度、 $P_l$ は発生損失である。

## 4. モデルベースの変換器の性能比較

#### 〈4·1〉 損失特性

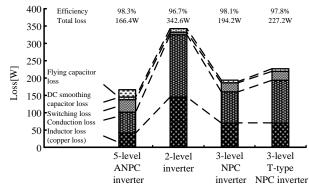

Fig.5 に Table1 の変換器の仕様を用いて計算した 4 つの変換器の損失特性及び効率を示す。Fig.5 において、3 相 10kW を定格として各変換器を設計し、定格運転時における検討を行なった。それぞれの効率は、5 レベル ANPC インバータが 98.3%、2 レベルインバータが 96.7%、3 レベル NPC インバータが 98.1%、3 レベル T-type NPC インバータが 97.8%となっており、5 レベル ANPC インバータの効率が、最も高いことがわかる。なお、損失の算定法は、これまで筆者らの検討により妥当性を確認している(4)。また、各変換器の損失に注目すると、全ての変換器において導通損失が支配的であることがわかる。

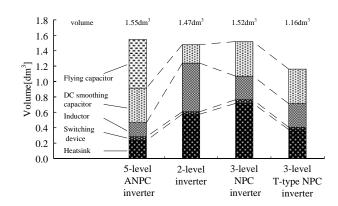

#### 〈4·2〉 体積比較

Fig.6に Table1 の条件を用いて系統連系インダクタを含めた各変換器の体積比較を行なった結果を示す。5 レベルANPCインバータが1.55dm³, 2 レベルインバータが1.47dm³, 3 レベル NPC インバータが1.52dm³, 3 レベル T-type NPC インバータが1.16dm³ となっている。3 レベル T-type NPC インバータが積が最も低く、その一方で、5 レベル ANPC インバータが最も体積が大きい変換器であることがわかる。しかし、5 レベル ANPC インバータは系統連系インダクタの体積を他の変換器よりも小型(2 レベルインバータの1/4、3 レベルインバータの1/2)にできる。また、5 レベル ANPC インバータのフライングキャパシタにフィルムコンデンサを使用することができるため、キャパシタ体積の低減が可能で

Fig.5. Loss analysis of the inverter topologies.

ある。

#### 〈4·3〉 パレートフロントによる比較

パレートフロントを用いて 4 つの変換器の比較を行う。 パレートフロントは変換器のスイッチング周波数を変化さ せたときのパワー密度と効率を軸にとったものであり,変 換器性能の指標を表す 1 つの考え方である<sup>(7)</sup>。

Fig.7 にスイッチング周波数を 1kHz から 1MHz まで変化させた時の各変換器のパレートフロントを示す。Fig.7 より 5 レベル ANPC インバータはスイッチング周波数が 30kHz のときパワー密度が 6.3kW/dm³, 効率が 98.2%になる。2 レベルインバータは、スイッチング周波数が 100kHz のときパワー密度が 8.6kW/dm³, 効率は 97.0%になる。3 レベル NPC インバータはスイッチング周波数が 40kHz のときパワー密度が 6.5kW/dm³, 効率が 98.1%になる。3 レベル T-type NPC インバータはスイッチング周波数が 100kHz のときパワー密度が 9.7kW/dm³, 効率が 97.7%になる。このことから、5 レベル ANPC インバータが最も高効率な変換器を設計可能である。また、3 レベル T-type NPC インバータが最も高パワー密度な変換器を設計可能である。

#### 5. 結論

本論文では、これまでに提案した変換器設計法を用いて太陽光発電系統連系用インバータとして 4 つの変換器トポロジーを設計し、パレートフロントによる性能比較を行なった。

5 レベル ANPC インバータが最も高効率な変換器を設計可能である,また,3 レベル T-type NPC インバータが最も高パワー密度な変換器を設計可能であることがわかった。

今後は、3 レベルトポロジーの実験による計算式の妥当性の確認、5 レベルにおける他のマルチレベル変換器との性能比較、また次世代デバイスを用いた場合の 5 レベル ANPC インバータの性能について比較、検討する予定である。

#### 文 献

- (1) F. Z. Peng: "A Generalized Multilevel Inverter Topology with Self Voltage Balancing", IEEE Transactions on industry applications, Vol.37, No.2, pp. 2024-2031 (2001)

- (2) Barbosa, P.; Steimer, P.; Steinke, J.; Meysenc, L.; Winkelnkemper, M.; Celanovic, N: "Active Neutral-point-Clamped Multilevel Converter", Power Electronics Specialists Conference, 2005. PESC '05. IEEE 36th 16-16 June 2005 Page(s):2296 – 2301

- (3) Lin Ma, Tamas Kerekes, Remus Teodorescu, Xinmin Jin, Dan Floricau, Marco Liserre: 「The High Efficiency Transformer-less PV Inverter Topologies Derived From NPC Topology」, EPE 2009-Barcelona, pp.1-10 (2009)

- (4) 樫原有吾, 伊東淳一: 「5 レベルアクティブ NPC インバータの最適設計に関する検討」, SPC 長野, SPC-10-124, 2010

- (5) Wm. T. Mclyman: "Transformer and inductor design handbook", Marcel Dekker Inc. (2004)

- (6) 大沼喜也, 伊東淳一:「単相三相変換器における昇圧チョッパ回路と アクティブバッファ回路の比較」, 電気学会全国大会, 4-042, 2011

- J. W. Kolar, J Biela and J, Minibock: 「Exploring the Pareto Front of Multi

-Objectice Single-Phase PFC Rectifier Design Optimization -99.2%

Efficiency vs. 7kW/dm³ Power Density」, IPEMC 2009-China, (2009)

Fig.6. Volume analysis of the inverter topologies.

Fig.7. Pareto front of the inverter topologies.

Table 1 the Converter specification and devices.

#### (a) converter specification

| Input voltage        | 350V             | Rated power         | 10kW  |

|----------------------|------------------|---------------------|-------|

| Output voltage       | 200V             | Output frequency    | 50Hz  |

| Output current       | 20A              | Switching frequency | 20kHz |

| Ripple Voltage       | Flying capacitor |                     | 3%    |

| (ANPC inverter only) | DC smo           | othing capacitor    | 5%    |

| Ripple Current       | Inductor         |                     | 5%    |

| CSPI                 | Heatsink         |                     | 10    |

#### (b) 5level ANPC inverter

| Cell1  | MOSFET:IRFP4668pBF(IR)        |

|--------|-------------------------------|

| Cell2  | MOSFET:IXFB170N30P(IXYS)      |

|        | LXS series (Nippon chemi-con) |

| action | 5 parallel connection         |

| thing  | LXS series (Nippon chemi-con) |

| or     | 5 parallel connection         |

|        | Cell2<br>acitor               |

#### (c) 2level inverter

| Switching device | IGBT:1MBH50D-060S (Fuji Electric) |

|------------------|-----------------------------------|

| DC smoothing     | LXS series (Nippon chemi-con)     |

| capacitor        | 5 parallel connection             |

|                  |                                   |

# (d) 3level NPC inverter

| Switching device | MOSFET:IXFB170N30P(IXYS)      |

|------------------|-------------------------------|

| DC smoothing     | LXS series (Nippon chemi-con) |

| capacitor        | 5 parallel connection         |

#### (e) 3level T-type NPC inverter

| Switching    | Cell1 | MOSFET:IXFB170N30P(IXYS)          |

|--------------|-------|-----------------------------------|

| device       | Cell2 | IGBT:1MBH50D-060S (Fuji Electric) |

| DC smoothing |       | LXS series (Nippon chemi-con)     |

| capacit      | or    | 5 parallel connection             |