# GaN-FET を用いた PWM インバータの EMC フィルタに関する実験検討

荒木 降宏\* 折川 幸司 伊東 淳一 (長岡技術科学大学)

Experimental Verification of an EMC Filter used for PWM Inverter Constructed by GaN-FET Takahiro Araki\*, Koji Orikawa, Jun-ichi Itoh (Nagaoka University of Technology)

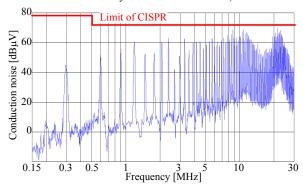

This paper discusses an EMC filter that is used for a PWM inverter constructed by GaN-FETs. First, the volume of inductor that is used for EMC filter such as common mode reactors and differential mode reactors are estimated by theoretically. Then, the relationship between the carrier frequency of the PWM inverter and the total volume filter reactors are clarified by simulation. Moreover, the relationship between the carrier frequency and the volume of a cooling system is calculated based on experimental result of loss analysis. As a result, the volume of PWM inverter that contains an EMC filter and a cooling system will be reduced by 53.4% at the carrier frequency is 300 kHz. In addition, a prototype of GaN-FET inverter is demonstrated by experiments. As a result, the conduction noise is suppressed below the limit of CISPR. Therefore, the proposed design method for EMC filters is valid in the experiment.

キーワード: EMC フィルタ、伝導ノイズ、高周波スイッチング、GaN-FET、PWM インバータ (Keyword: EMC filter, Conduction noise, High-frequency switching, GaN-FET, PWM inverter)

## 1. はじめに

近年,モータ駆動システムなどに使用される PWM インバ ータは小形化が求められている。それに伴い電力変換回路 の小形化が進められる一方で、システム全体における EMC フィルタの体積が相対的に増加している。したがってシス テム全体の小形化にはEMCフィルタの体積を含めた検討が 必要である。EMC フィルタの体積はノイズの周波数や減衰 量などに依存する。また、PWM インバータで発生するノイ ズはキャリア周波数により変化する。したがってキャリア の高周波化によりノイズの周波数と減衰量を変化させるこ とで EMC フィルタの小形化が可能である。その反面、キャ リアの高周波化に伴いスイッチング損失が増加する。損失 の増加は冷却装置の大形化を招くため、 高周波化により EMC フィルタの小形化を行う場合は冷却装置の体積も合わ せて検討する必要がある。著者らはこれまでに EMC フィル タと冷却装置の合計体積が最小となるキャリア周波数につ いて検討を行った。その結果キャリア周波数を300kHzに設 定することで合計体積が最小となる見込みを得ている(1)。 一方, 近年では電気機器の省エネルギー化が要求され, PWM インバータには更なる高効率化が求められている。イ ンバータの効率を向上させるためには導通損失とスイッチ ング損失の低減が必要である。これらを同時に達成する手 段として高性能なスイッチング素子の使用が挙げられる。 特にキャリア周波数 300 kHz という高周波での動作を実現

したがって提案システムにはオン抵抗が小さく高速スイッチング可能なスイッチング素子が求められるが、現在使用されているシリコンデバイスは物性値に由来する性能限界に達しつつあるため、性能の大幅な向上は困難であると考えられている<sup>(2)</sup>。それに対して近年ではシリコンカーバイド(SiC)やガリウムナイトライド(GaN)などのワイドバンドギャップ半導体を用いたスイッチング素子が盛んに研究されている。これらは従来のシリコンデバイスと比較し、低損失、高速スイッチング、高耐圧などの優れた動作特性が確認されており、注目されている<sup>(3)-(5)</sup>。これまでにワイドバンドギャップ半導体の優位性は主に、効率や高温動作について多く報告されているが、システム体積やパワー密度の

観点から論じられた論文は少ない。

するためにも高速なスイッチングが必要不可欠である。

本論文では GaN-FET を用いた PWM インバータシステムについて、キャリア周波数と効率、および体積の関係を実験結果に基づき検討した。なお、インバータの効率と体積はトレードオフの関係にあるため、パレートフロントカーブを用いて評価した。その結果、EMC フィルタの段数を2段に、キャリア周波数を300kHzに設定することでパワー密度が最高となる見込みを得た。また、GaN-FET を用いてキャリア周波数300kHzで動作するPWM インバータを試作し、雑音端子電圧を測定した。そして設計した EMC フィルタにより雑音端子電圧が CISPR の規制値以下に抑制されることを確認した。

## 2. パワー密度の理論的検討

## 〈2·1〉 電力変換回路の損失

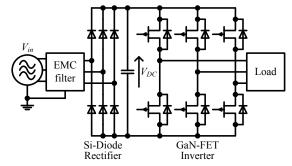

図 1 に提案システムの構成図を示す。まず、PWM インバータの各スイッチング素子で発生するスイッチング損失  $P_{SW}$  は(1)式で求められる $^{(6)}$ 。

$$P_{SW} = \frac{V_{DC}I_m}{4\pi V_{DCd}I_{md}} \left(e_{on} + e_{off}\right) f_{carrier} \qquad (1)$$

ここで、 $V_{DC}$ :直流電圧、 $I_m$ :出力電流最大値、 $e_{on}$ および  $e_{off}$ :1 回のスイッチングで発生するターンオン損失およびターンオフ損失、 $V_{DCd}$ および  $I_{md}$ :データシート上のスイッチング時間測定条件の電圧および電流、 $f_{carrier}$ :キャリア周波数である。

PWMインバータで発生する損失 $P_{loss}$ はスイッチング損失と導通損失 $P_{CON}$ の合計であり、(2)式により求められる。

$$P_{loss} = 6(P_{SW} + P_{CON}) = 6\left(P_{SW} + \frac{I_m^2}{2}R_{ON}\right) \cdots (2)$$

ここで  $R_{ON}$ :FET のオン抵抗である。

## 〈2·2〉 冷却装置の体積

一般的に冷却装置は熱抵抗に基づき設計されるが、熱抵抗は体積に依存する。そこで本論文では単位体積あたりの冷却性能を示す CSPI(Cooling System Performance Index)を用いて評価する。 CSPI は体積と熱抵抗の積の逆数であり、熱抵抗、上昇温度、損失の関係から冷却装置体積 volcooling は(3)式で求められる<sup>(7)</sup>。

$$vol_{cooling} = \frac{1}{R_{th} \times CSPI} = \frac{P_{loss}}{\left(T_{j} - T_{a}\right) \times CSPI} \cdots (3)$$

ここで、 $R_{th}$ :冷却装置の熱抵抗、 $T_{j:}$ スイッチング素子のジャンクション温度、 $T_{a}$ :冷却装置の周囲温度である。

# 〈2·3〉 EMC フィルタの体積

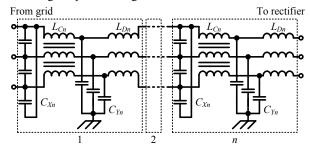

図2にEMCフィルタの回路図を示す。フィルタ体積を検討するにあたり、まずはフィルタの設計を行う。

はじめに X コンデンサ  $C_{Xn}$  は軽負荷時に力率の悪化を招くため、許容される最大電流進み角を用いて(4)式で計算される。

$$C_{Xn} = \frac{\sqrt{3}kI_{in}\phi}{n\omega V_{in}} \qquad (4)$$

ここで、k:負荷率(出力電力/定格電力)、 $I_{in}$ :入力電流、 $\phi$  最大電流進み角、n:フィルタ段数、 $\omega$ :入力角周波数、 $V_{in}$ :入力電圧である。

次にY コンデンサ $C_{Yn}$ は許容される漏れ電流値に基づき(5)式で計算される。

$$C_{\gamma_n} = \frac{\sqrt{3}I_{kak}}{n\omega V_{\infty}} \tag{5}$$

ここで $I_{leak}$ :漏れ電流である。

ディファレンシャルモード用リアクトル  $L_{Dn}$  とコモンモード用リアクトル  $L_{Cn}$  は EMC フィルタを接続しない条件で CISPR の規制値  $G_f$ を大きく超えた低い周波数 $\omega_{An}$ とそのゲ

Fig.1. System configuration of GaN-FET inverter.

Fig.2. Circuit diagram of an EMC filter.

イン $G_0$ を用いてLCフィルタの減衰率から(6)式により設計される。なお、各ノイズは文献8の回路により分離する。

$$L_n = \frac{1}{\omega_{Att}^2 C_n (G_0 - G_f)^{\frac{1}{n}}}$$

(6)

本論文では素子パラメータの変化に対して体積の増減が大きいリアクトルに着目して検討する。リアクトルのコアの選定方法はいくつかの方法があるが、ここではコアの窓面積と断面積の積によりコアを選定する Area Product<sup>(9)</sup>の考え方に基づきリアクトルを設計する。このとき、リアクトルの体積 vol, は(7)式により求められる。

$$vol_{L} = K_{v} \left( \frac{2W}{K_{u}B_{m}J} \right)^{\frac{3}{4}} \dots (7)$$

ここで、 $K_{\nu}$ :コア形状定数、W:リアクトルの最大蓄積エネルギー、 $K_{u}$ :窓の占積率、 $B_{m}$ :コアの最大磁束密度、J:巻線の電流密度である。

### 3. 検討条件

# 〈3·1〉 EMC フィルタの設計

表1に設計で使用したパラメータを示す。2.3章の手順に沿って EMC フィルタを設計する場合,はじめに EMC フィルタを接続しない状態で雑音端子電圧を観測する必要がある。しかし雑音端子電圧は電力変換回路の浮遊容量や配線インダクタンスなど,測定環境に依存するパラメータにより変化する。そのため実際の回路を用いて測定した場合は再現性が悪く,定量的に評価することが困難である。したがって本論文ではシミュレーションによって雑音端子電圧を推定する。

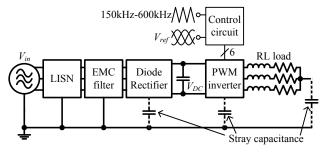

図3に雑音端子電圧の推定に使用する提案システムのシミュレーションモデルを示す。ノイズの発生原因となる浮

遊容量は、ダイオード整流器と PWM インバータの直流リンク部と対地間、および負荷中性点と対地間の成分をモデル化する $^{(10)}$ 。また、測定にはモデル化した LISN(Line Impedance Stabilization Network)を使用し、観測された雑音端子電圧にスペクトルアナライザと同様のデータ処理を行う $^{(11)}$ 。

PWM インバータのゲート信号は三角波比較法を用いて 三相変調により生成する。なお、GaN-FET で構成した場合 を想定し、各素子のゲート信号には 100 ns のデッドタイム を付加する。また、インバータはオープンループで制御し、 デッドタイム誤差補償は行わない。これはキャリア周波数 を変更した場合も同様である。

なお、EMC フィルタで発生する損失はインバータ損失に対して非常に小さいため検討しない。

# 〈3·2〉 GaN-FET インバータの効率測定

表 2 に実験条件を示す。PWM インバータは GaN-FET ( $V_{DSmax}$ =600 V,  $I_{Dmax}$ =10 A,  $R_{ON}$ =100 m $\Omega$ )を用いて構成した。インバータの効率は直流部と出力部の電力をパワーメータにより測定し,その差分からインバータの損失を求めることで評価する。その際,キャリア周波数を 150 kHz から 600 kHz まで変更することで,導通損失とスイッチング損失の損失分離を行う。キャリア周波数を変更する際は,シミュレーションと同様にスイッチング速度やデッドタイムを一定とする。

## 4. パワー密度の検討結果

# 〈4·1〉 フィルタリアクトル体積

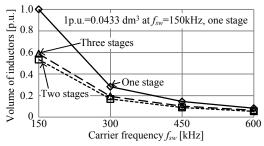

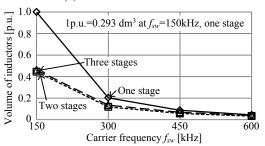

図 4(a)にキャリア周波数とディファレンシャルモードリアクトル体積の関係を、図 4(b)にキャリア周波数とコモンモードリアクトル体積の関係を示す。それぞれの結果はフィルタ段数が1段、キャリア周波数が150 kHz の場合を基準としており、この条件で各リアクトル体積は最大となる。これはCISPRによって150 kHz から30 MHz の雑音端子電圧が規制されているためであり、規制周波数領域の下限周波数とキャリア周波数が一致するこの条件においては、キャリア周波数の基本波成分によって発生する雑音端子電圧をEMCフィルタにより抑制しなければならないためである。

図 4(a)と図 4(b)の結果より、キャリアの高周波化によりフィルタリアクトルの小形化が可能である。これはフィルタ 段数に依らず同様の傾向を示す。また EMC フィルタを多段化した場合もそれぞれのリアクトルは小形化される。特にキャリア周波数が 150 kHz の場合は、1 段から 2 段に多段化することで各リアクトルの体積をおよそ半分に低減することが可能である。更にフィルタの多段化によるリアクトルの小形化はキャリアの高周波化を伴わないため、スイッチング損失が増加せず、効率の観点からも有利である。その反面、フィルタの段数に比例して EMC フィルタを構成するコンデンサやリアクトルなどの部品点数が増加する。そのため、それぞれのリアクトル体積はフィルタの段数を 2 段に設計した際に最小となり、フィルタの段数を 3 段に設計した場合は大形化した。

Table 1. Simulation parameters

| Input voltage $V_{in}$            | 200 V                  |

|-----------------------------------|------------------------|

| Input frequency $f_{in}$          | 50 Hz                  |

| DC voltage $V_{dc}$               | 282 V                  |

| Output voltage $V_{out}$          | 173 V                  |

| Output current $I_{out}$          | 1.88 A                 |

| Output frequency $f_{out}$        | 20 Hz                  |

| Load impedance $Z_{load}$         | 53.2 Ω                 |

| Power factor $\cos \phi$          | 0.998                  |

| Modulation ratio $\alpha$         | 1                      |

| CSPI                              | 3                      |

| On-resistance $R_{ON}$            | $100~\mathrm{m}\Omega$ |

| Dead time $T_d$                   | 100 ns                 |

| Ambient temperature $T_a$         | 20 ℃                   |

| Junction temperature $T_j$        | 100 ℃                  |

| Load factor k                     | 0.1                    |

| Lead angle $\phi$                 | 10π/180 rad            |

| Leakage current I <sub>leak</sub> | 1 mA                   |

Fig.3. Conduction noise evaluation system.

Table2. Experimental conditions of GaN-FET inverter.

| DC link voltage $V_{DC}$   | 140 V  |

|----------------------------|--------|

| Modulation ratio $\alpha$  | 1      |

| Output frequency $f_{out}$ | 20 Hz  |

| Load impedance $Z_{load}$  | 51 Ω   |

| Power factor $\cos \phi$   | 0.99   |

| Ambient temperature $T_a$  | 25 ℃   |

| Dead time $T_d$            | 100 ns |

(a) Differential mode reactor

(b) Common mode reactor Fig.4. Volume of filter reactor.

なお、キャリアを 600 kHz まで高周波化した場合はフィルタの段数に依らず各リアクトルの体積はほぼ等しく、多段化による体積低減効果は小さい。この場合、フィルタの多段化は部品点数の増加による大形化や実装面積の増加を招くため有用ではない。

## 〈4·2〉 PWM インバータの損失

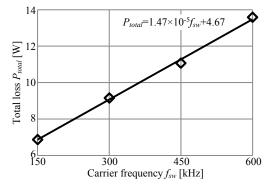

図 5 に GaN-FET を用いて構成した PWM インバータの効率測定結果を示す。表 2 の条件で試験した際の出力電力はおよそ 130 W であり、キャリア周波数が 150 kHz の際に最高効率の 94.7%を観測した。

PWM インバータで発生する導通損失はキャリア周波数に依存せず一定のため、近似直線の切片から 4.67~W と求められる。つまり各 GaN-FET の導通損失は 0.778W であり、出力電流を用いて(2)式により計算される等価的なオン抵抗は  $800~m\Omega$ である。これはデータシートに記載された  $100~m\Omega$  と比較して非常に大きいが、GaN-FET の電流コラプス現象が原因であると考えられる。

一方,スイッチング損失はキャリア周波数に比例するため,近似直線の傾きから計算可能である。測定結果より PWM インバータの出力電力を変化させた場合の導通損失は(2)式を変形した(8)式により求められる。

$$P_{CON} = b \times \left(\frac{I_{out\_calc}}{I_{out\_test}}\right)^{2} \dots (8)$$

ここで、b:近似直線の切片, $I_{out\_calc}$ :任意の出力電力における出力電流実効値, $I_{out\_test}$ :損失測定時の出力電流実効値である。

同様にスイッチング損失は(1)式を変形した(9)式で計算される。

$$P_{SW} = a f_{carrier} \frac{V_{DC\_calc}}{V_{DC\_test}} \frac{I_{out\_calc}}{I_{out\_test}} \cdots (9)$$

ここで、a:近似直線の傾き、 $V_{DC\_calc}$ :任意の出力電力における直流リンク電圧、 $V_{DC\_test}$ :損失測定時の直流リンク電圧である。

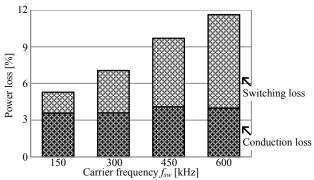

図 6 に試作した GaN-FET インバータの損失解析結果を示す。試作した PWM インバータはキャリア周波数が 300 kHz の際に導通損失とスイッチング損失の割合がほぼ等しくなり,300 kHz 以下では導通損失が,300 kHz 以上ではスイッチング損失が支配的である。導通損失が支配的な周波数領域では,キャリアの高周波化によりスイッチング損失が増加した場合でも合計損失には大きな影響を及ぼさない。そのため,この周波数領域では冷却装置体積の僅かな増加でフィルタリアクトル体積を大幅に低減できる可能性がある。

したがって提案システムには導通損失よりもスイッチング損失が小さい PWM インバータが適している。 PWM インバータの導通損失とスイッチング損失の割合はスイッチング素子の特性に依存する。 すなわち提案システムは高速なスイッチングによりスイッチング損失が小さい GaN-FET の優位性を活かすことが可能である。

Fig.5. Measurement result of relationship between carrier frequency and power loss of GaN-FET inverter.

Fig.6. Loss analysis result of GaN-FET inverter.

Fig.7. Calculation result of relationship between carrier frequency and power loss of GaN-FET inverter.

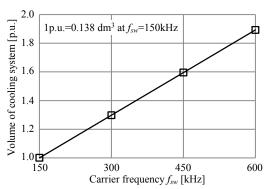

## 〈4・3〉 冷却装置の体積

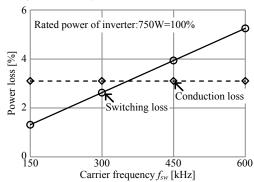

図7にGaN-FETインバータを定格出力の750Wで運転した場合を想定した損失解析結果を示す。定格運転時は出力電流が増加し、導通損失はその2乗に比例して大幅に増加する。一方、スイッチング損失は出力電流に比例するため、定格運転時は導通損失がより支配的となる。したがってPWMインバータの大容量化は、キャリアの高周波化によりフィルタリアクトルを小形化する上で有利に働く。なお、定格運転時の効率はキャリア周波数が150kHzの時に最大で95.6%になる。

図8にキャリア周波数と冷却装置体積の関係を示す。キャリアを高周波化した場合、スイッチング損失が比例して増加するため大形の冷却装置が必要となる。しかし、試作した GaN-FET インバータは導通損失が支配的なため、冷却装置体積への影響は小さい。そのためキャリア周波数を 150

kHzから4倍の600 kHzに高周波化した場合でも冷却装置体積は2倍以下である。

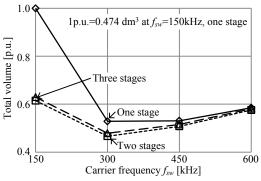

#### 〈4·4〉 合計体積

図9にキャリア周波数と合計体積の関係を示す。ここで合計体積とはフィルタリアクトルと冷却装置を合計した体積であり、他の部品はキャリア周波数によって体積が変化しないため考慮しない。

キャリアを高周波化した場合,300 kHz まではフィルタリアクトルが小形化されることにより合計体積も減少する。そのため EMC フィルタを1段で構成した場合はキャリア周波数を150 kHz から300 kHz に高周波化することで合計体積を半分に低減可能である。しかし300 kHz 以上の領域では冷却装置が大形化することにより合計体積は増加する。

一方, EMC フィルタを多段化した場合,キャリア周波数が低い領域ではフィルタリアクトルが小形化されるため合計体積も40%近く低減される。だがキャリア周波数が高い領域では既に EMC フィルタが小形化されている上,冷却装置体積が大きな割合を占めているため効果がない。

以上の傾向より、フィルタ段数が2段、キャリア周波数が300kHzの時に合計体積は53.4%低減され最小となる。

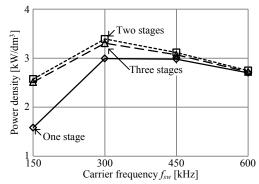

#### 〈4·5〉 パワー密度

図 10 にキャリア周波数とパワー密度の関係を示す。パワー密度 $\rho_{power}$  は単位体積あたりの出力電力を示しており、このパラメータが大きいほど高効率かつ小形な電力変換回路であることを意味する。

本論文では GaN-FET インバータの定格電力  $P_{out}$ , および フィルタリアクトルと冷却装置の合計体積を用いて(10)式 で定義する。

$$\rho_{power} = \frac{P_{out}}{vol_{total}}$$

(10)

(10)式よりパワー密度は合計体積に反比例するため、キャリアの高周波化に伴い合計体積が低減されることでパワー密度は向上する。そして合計体積が最小となるキャリア周波数が 300 kHz の際にパワー密度は最大となる。なお、キャリアを 300 kHz 以上に高周波化した場合は合計体積の増加によりパワー密度が低下する。そのため 300 kHz 以下のキャリア周波数でも同一のパワー密度が達成可能である。したがって PWM インバータの効率を考慮するとスイッチング損失の増加を招く 300 kHz 以上のキャリア周波数は使用するべきではない。

またフィルタ段数毎のパワー密度を比較すると、多段フィルタを使用している場合はキャリア周波数の変化に対してパワー密度の変動幅が小さい。したがってキャリアの高周波化による EMC フィルタの小形化は1段の EMC フィルタを設計する際に最も効果的である。一般に多段 EMC フィルタは部品点数の増加に伴い設計が複雑になるため、提案システムの適用により1段の EMC フィルタでも同等のパワー密度を達成できる場合、フィルタ設計の簡素化が可能で

Fig.8. Relationship between carrier frequency and volume of cooling system.

Fig.9. Relationship between carrier frequency and total volume of GaN-FET inverter system.

Fig.10. Relationship between carrier frequency and power density of GaN-FET inverter.

ある。なおパワー密度は、フィルタ段数が 2 段、キャリア周波数が  $300~\rm{kHz}$  の時に最大で  $3.39~\rm{kW/dm}^3$  となる。

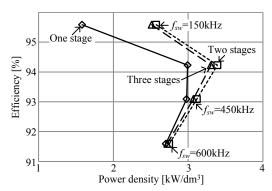

## 〈4.6〉 パレートフロントによる評価

図 11 にキャリア周波数を 150 kHz から 600 kHz まで変化させた場合のパレートフロントカーブを示す。パレートフロントは複数の目的に対して最適な解を求めるための手段であり、本手法を用いることで電力変換回路の効率と体積というトレードオフの関係にある 2 つのパラメータを同時に評価することが可能である。図 11 では横軸がパワー密度、縦軸が効率を示しており、右上に近づくほど高効率で小形な優れた電力変換回路であることを意味する。

結果よりフィルタ段数は2段に設計するべきであり、パワー密度を重視する場合はキャリア周波数を300kHzに、効率を重視する場合はキャリア周波数を150kHzに設計することで最適な設計が可能となる。

# 5. 雑音端子電圧の評価

#### 〈5·1〉 測定条件

これまでの検討において設計した EMC フィルタパラメータの妥当性を検証するため、GaN-FET を用いて試作した PWM インバータを使用して雑音端子電圧を測定する。その際、インバータを構成する GaN-FET は 1 枚の基板上に上下アーム分の 2 素子を実装し、これを 3 枚使用する。また、整流器とインバータは別々のヒートシンクに設置する。

なおシミュレーションでは電力変換回路で発生する雑音 端子電圧のみを評価しているため、インバータシステム全 体で発生する雑音端子電圧から、主回路停止時に発生する 雑音端子電圧を差し引くことで条件を一致させて評価する。

#### 〈5·2〉 測定結果

図 12(a)に試作した GaN-FET インバータをキャリア周波数 300 kHz で動作させた場合の雑音端子電圧を示す。なお、測定の際は設計した 2 段の EMC フィルタを使用している。その結果、キャリア周波数とその整数倍にピークが存在するものの、雑音端子電圧は全周波数領域において赤線で示す CISPR の規制値以下に抑えられており、設計した EMC フィルタパラメータの妥当性を確認した。

図 12(b)に 1 段の EMC フィルタを使用した場合の結果を示す。なお、本フィルタは 300 kHz において 2 段の EMC フィルタと同等の減衰率が得られるように設計した。その結果、300 kHz では図 12(a)と同様に雑音端子電圧が設計通りに抑制された。一方、9 MHz 付近では CISPR の規制値を 10 dB 超過した。これは EMC フィルタが 1 段で構成されているため、2 段の場合と比較して高周波領域の減衰量が小さいためである。

## 6. まとめ

本論文では GaN-FET を用いた PWM インバータのキャリア周波数と効率、および体積の関係を実験結果に基づき検討した。その結果、キャリア周波数を 300 kHz に設定することでパワー密度が最高となる見込みを得た。更に、GaN-FETを用いてキャリア周波数 300 kHz で動作する PWM インバータを試作し、雑音端子電圧を測定した。そして設計した EMCフィルタにより雑音端子電圧が CISPR の規制値以下に抑制されることを確認した。

#### 文 献

- (1) 荒木隆宏, 伊東淳一:「ワイドバンドギャップデバイスを用いたモータドライブ用 PWM インバータの基礎検討」, SPC-12-126, EDD-12-53 (2012)

- (2) 荒井和雄, 吉田貞史, 共編: 「SiC 素子の基礎と応用」, オーム社(2003)

- (3) 中林 幸久, 藤崎 誠司, 寺園 勝志, 原 秀則, 井手 幸三:「高パワー密度 AC-AC コンバータの開発」, 平成 24 年度電気学会産業応用部門大会, Vol.1, 1-01-2 (2012)

- (4) 酒井 雅弘,滝口 昌司,小山 考,小太刀 圭一,小倉 和也:「SiC15kVA インバータの特性評価」,平成 24 年度電気学会産業応用部門大会, Vol.1, 1-01-4 (2012)

- (5) 松井康平,佐々木健介,谷本智,村上善則,谷澤秀和,佐藤伸二: 「70kW/L All-SiC インバータの開発」,平成25年電気学会全国大会,Vol.4,p.252(2013)

- (6) Yugo kashihara, Jun-ichi Itoh, "The performance of the

Fig.11. Pareto front curve of GaN-FET inverter. (Relationship between power density and efficiency of GaN-FET inverter)

(a) Two stages filter.

80

Limit of CISPR

20

0.15

0.3

0.5

1

3

5

10

30

Frequency [MHz]

(b) One stage filter. Fig.12. Conduction noise of the GaN-FET inverter using 300 kHz carrier with designed EMC filter.

multilevel converter topologies for PV inverter", International Conference on Integrated Power Electronics Systems 2012, pp.67-72(2012)

- (7) Uwe DROFENIK, Gerold LAIMER, Johann W. KOLAR: "Theoretical Converter Power Density Limits for Forced Convection Cooling", Proceedings of the International PCIM Europe Conference, pp.608-619 (2005)

- (8) J. Kolar, H. Ertl: "Vorrichtung zur trennung der funkstoerspannungen dreiphasiger stromrichtersysteme in eine gleich-und eine gegentaktkomponente" (in german), Patent Swiss Patent Application, (2004)

- (9) Wm T Mclyman: "Transformer and inductor design handbook", Marcel Dekker Inc. (2004)

- (10) M. Hartman, H. Ertl, J. W. Kolar: "EMI filter design for high switching frequency three-phase/level PWM rectifier systems" Applied Power Electronics Conference and Exposition 2010, pp.986-993(2010)

- (11) M. L. Heldwein, T. Nussbaumer, J.W.Kolar: "Differential Mode EMC Input Filter Design for Three-Phase AC-DC-AC Sparse Matrix PWM Converters" Power Electronics Specialists Conference, pp.284-291(2004)