# マルチコアトランスと多相インバータを用いた MHz 級高周波電源の損失解析

折川 幸司\* 伊東 淳一(長岡技術科学大学)

Loss Analysis of MHz Power Supply Constructed from Multi-Core Transformers and a Multi-Phase Inverter Koji Orikawa\*, Jun-ichi Itoh, (Nagaoka University of Technology)

This paper describes the power loss analysis of MHz power supply which consists of a multi-phase inverter and multiple core transformers. In this paper, bifilar wound transformers and a LC series resonance are applied to the proposed circuit in order to achieve higher output power. The current and the power loss in each circuit element are formulated in order to clarify the power loss distribution of the proposed circuit. Finally, the relationship between the power loss, the number of phase in inverter was clarified.

**キーワード**: 高周波電源, マルチコアトランス, 漏れインダクタンス, 直列共振, 損失解析 (High frequency power supply, Multiple core transformer, Leakage inductance, Series resonance, Loss analysis)

## 1. はじめに

近年、電気自動車用バッテリの非接触充電装置や半導体製造用プラズマ発生電源装置、誘導加熱装置用にMHz帯の周波数を出力する高周波電源の使用が検討もしくは実際に使用されており、それらの高周波電源の高効率化・小型化が要求されている(1)-(8)。従来の高周波電源装置は真空管やパワーMOSFETなどの半導体素子を用いたC級リニアアンプ方式で構成されることが多い。そのため、原理的に効率が低く、ヒートシンクやファンなどの放熱機器を付加する必要があり、システムが大型となる。また、真空管方式では素子の寿命が短いため信頼性が低い問題がある。

一方、IGBTや MOSFET などの電力変換用半導体素子は、近年性能が向上し低損失化、大容量化が進んでいる。さらに、近年の半導体デバイス技術の進歩により、SiC や GaN などの高速スイッチング可能でかつ低損失なワイドバンドギャップ半導体デバイスが広く使われ始めている。しかしながら、ゲートドライブ回路の消費電力の増加や低ゲート 閾値電圧によってゲート駆動回路の制御が困難になることやゲート駆動回路の実装が困難になるといった問題がある(5)-(7)。例えば、高周波スイッチングノイズによる自己誤点弧やサージ電圧の増加による電圧ストレスの増大がある。このように、ワイドバンドギャップ半導体デバイスを使用した高周波電力変換器にはいくつかの問題があり、ワイドバンドギャップ半導体は依然、従来素子と比べて高価であり、電源の高コスト化が問題である。

この結果,特に大容量高周波電源の小型化や高効率化が困難とされている。

そこで、著者らはこれまでに多相インバータの中性点電 位変動に注目しマルチコアトランスを組み合わせた回路構 成で周波数を逓倍できる方法について検討している(9)(10)。こ れまでに、実験により、本方式を 5 相インバータに適用す ることで、高速スイッチング可能な素子を使用せずに、MHz 帯の高周波出力を達成できることを確認した。また、提案 回路ではトランスの漏れインダクタンスと巻線抵抗および 負荷抵抗の関係で決まる時定数が短いことによってインバ ータ出力電圧の一部が欠ける現象(以降,パルス欠け,と 定義する) が発生することや定電流源動作となる問題を確 認し、その発生原理について等価回路による解析と実機実 験によって明らかにした。さらに、トランス二次側に直列 に共振キャパシタを接続することで, トランスの漏れイン ダクタンスを積極的に利用した直列共振回路による高出力 化を確認している。しかし、これまでに回路の損失を考慮 した回路設計に関する検討はされておらず、更なる高効率 化および高周波化のための検証が不十分であった。

本論文では、インバータの相数と回路損失の関係を定量的に明らかにすることを目的とする。損失解析の結果、直列共振における提案回路では、スイッチング損失はゼロであるが、インバータ損失およびトランスの銅損はインバータの相数に比例して増加することを確認した。一方、共振コンデンサの容量はトランスの漏れインダクタンスを含むインダクタンス成分および相数に反比例することを明らかにした。これらより、損失解析をもとに提案回路の設計指

針を把握することが可能であることを確認したので報告す る。

## 2. 提案回路

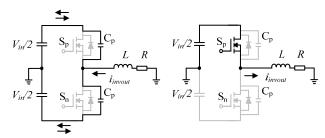

## 〈2:1〉周波数逓倍回路の原理

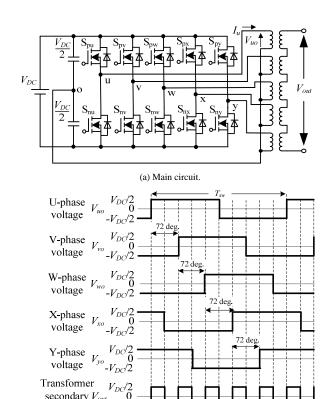

図 1(a)に 5 相電圧形インバータにマルチコアトランスを 接続し、トランス一次側を並列に、二次側を直列接続した 回路構成を示す。5相電圧形インバータは、各相の電圧指令 をそれぞれ72度ずつ位相シフトさせて方形波駆動する。

図 1(b)に、提案回路の周波数逓倍の原理図を示す。各トラ ンス一次側電圧は位相のずれた方形波であり, 本論文のマ ルチコアトランスでは、トランス二次側を直列接続するた め、インバータの相数、つまりトランスの段数を N とする とトランス二次側の出力周波数foutはインバータのスイッチ ング周波数 $f_{sw}$ を用いて(1)式で表される。

$$f_{out} = Nf_{sw}$$

(1)

したがって、出力周波数  $f_{out}$  を 2.5MHz、インバータを 5 相 (N=5) で設計する場合,スイッチング周波数  $f_{sw}$  は 500 kHz となる。表 1 に実際に製作したトランスのパラメータを示 す。

## 〈2·2〉マルチコアトランス

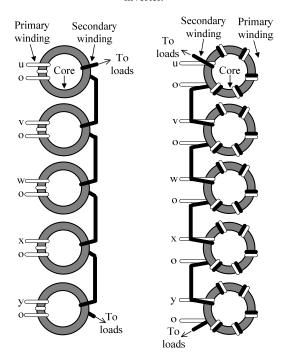

図2に実験に使用したマルチコアトランスを示す(11)(12)。 コアには、トロイダルコアを使用する。配線長を短くし巻 線の銅損を低減する方法にトランスの二次側の貫通巻があ る(10)。貫通巻では、トランスの一次側と二次側の結合度が 低下し、二次側漏れインダクタンスが大きくなる。一方、 バイファイラ巻は,一次巻線と二次巻線を撚ってコアに巻 くことで結合を高めることができる。通常のバイファイラ 巻では巻数比が 1:1 となるが, 本論文では直流電圧と同じ出 力電圧を実現するため、二次巻線を 2 本用意して合計 3 本 の撚り線とすることで、巻数比1:2を実現する。トロイダル コアには高周波領域で低損失であるフェライトコア(TDK 製, PC40 T38×14×22)を使用する。

## 3. パルス欠けの発生とその原因

## 〈3・1〉提案回路の等価回路

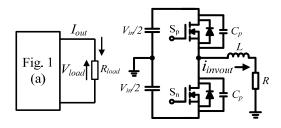

図 3(a)に提案回路に純抵抗を接続した場合の回路構成, 図 3(b)にその一相等価回路を示す。提案回路の一相等価回路 は、ハーフブリッジ回路となる。Lはトランス1次側から見 たトランスの漏れインダクタンスを含むインダクタンス成 分, R はトランス一次側から見たトランスの巻線抵抗および 負荷抵抗を含む抵抗成分である。また、 $C_p$ は MOSFET のド レイン・ソース間の寄生容量である。ここでは、バイファ イラ巻を前提条件とし、マルチコアトランスの励磁インダ クタンスは漏れインダクタンスよりも十分大きいとし,無 視している。また、多相インバータを一相等価回路にて解 析を行うため、図 3 の一相等価回路のスイッチング周波数 は出力周波数と等しい。

図4にハーフブリッジ回路の上側スイッチ $S_p$ がOFFから

(b) Principle of the proposed circuit (Turn ratio=1:1).

secondary  $V_{oi}$

voltage

Fig. 1. Multiplying frequency circuit using five-phase inverter.

(a) Secondary wiring through cores.

(b) Bifilar wound transformer.

Fig. 2. Multi-core transformer.

ON に切り替わるまでの動作モード図を示す。図 4(b),(c)に 上下スイッチが OFF するデッドタイム期間を示す。パルス 欠けが発生する場合には図 4(a)(b)(c)(d), パルス欠けが発生 しない場合には図 4(a)(b)(d)の順番で動作モードが変化す る。

図 4(b)に示す動作モードの回路方程式より、インバータの出力電圧にパルス欠けが発生しない条件はインバータのデッドタイム  $T_d$  を用いて、(2)式で表される。なお、直流コンデンサ電圧はスイッチング 1 周期中一定であると仮定する。

$$T_d < \frac{\tau}{N} \ln \left( \frac{2}{1 + \rho^{-\frac{T_{out}}{2\tau}}} \right) \dots (2)$$

ここで, $\tau=L/R$ :時定数(s), $T_{out}=1/f_{out}$ :出力周期(s),である。

(2)式より、パルス欠けの発生しない条件は、デッドタイム  $T_d$ 、時定数 $\tau$ 、スイッチング周期  $T_{sw}$ で決まることがわかる。ここで負荷を一定と仮定すると、漏れインダクタンスが小さい場合、時定数が小さくなり、(2)式を満足できなくなり、インバータ出力電圧にパルス欠けが発生する。その一方で、漏れインダクタンスが大きすぎても、提案回路は定電流源動作となり、出力電圧を一定に制御できなくなるという問題が発生する。したがって、提案回路において所望の出力電圧を出力するためには、パルス欠けが発生することなく、かつ定電圧動作を実現可能な適切な漏れインダクタンスに設計することが重要となる。しかし、適切な漏れインダクタンスに設計するだけでは提案回路の高出力化に限界がある。そのため、本論文では積極的に漏れインダクタンスを利用した LC 共振を用いた提案回路を扱う。

# 4. LC 共振による高出力化の原理

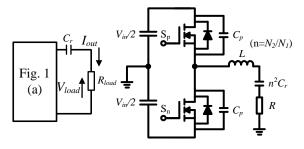

提案回路は、トランスの漏れインダクタンスを積極的に利用する直列共振により高出力化を実現できる<sup>(13)</sup>。提案回路では、トランス二次側に直列のコンデンサを接続することで、直列LC共振を実現する。

## 〈4·1〉共振コンデンサ

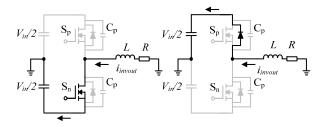

図 5 に提案回路のトランス二次側に直列に共振コンデンサを接続した回路と、その単相等価回路を示す。このとき、直列共振を実現するための共振コンデンサC,は、トランス一次側から見たインピーダンスの虚部がゼロとなる条件より(4)式で表される。

$$C_r = \frac{1}{(2\pi f_r)^2 L n^2}$$

(3)

ここで、 $f_r$ :共振周波数、n:トランスの巻数比である。

(3)式より、共振コンデンサの容量は、インバータの相数とトランスの漏れインダクタンスを含むインダクタンス成分に反比例することがわかる。したがって、共振コンデンサの容量を低減し、小型化する観点から、1)相数が多く、2)トランスの漏れインダクタンスが大きいことが好ましい。しかし、共振コンデンサの容量をトランスの巻線間の容量を無視できなくなるほど小さくしすぎると、共振状態を実現することが困難となるため、共振コンデンサの適切な設計が必要である。また、共振コンデンサには出力と同じ周波数を持つ電流が流れるため、高周波において特性の良い

Table 1. Parameters of transformer.

| Parameter                    | Symbol      | Rating         | Unit |

|------------------------------|-------------|----------------|------|

| Primary leakage inductance   | $L_{pwire}$ | 0.33           | μН   |

| Secondary leakage inductance | $L_{swire}$ | 0.49×2         | μΗ   |

| Magnetizing inductance       | М           | 92.2           | μΗ   |

| Primary winding resistance   | $R_{pwire}$ | 0.4            | Ω    |

| Secondary winding resistance | $R_{swire}$ | $0.4 \times 2$ | Ω    |

(a) Experimental circuit.

(b) Single-phase equivalent circuit.

Fig. 3. Proposed circuit.

(a) S<sub>p</sub>:OFF, S<sub>n</sub>:ON.

(b) Sp:OFF, Sn:OFF(After (a)).

(c) S<sub>p</sub>:OFF, S<sub>n</sub>:OFF(After (b)).

(d) S<sub>p</sub>:ON, S<sub>n</sub>:OFF.

Fig. 4. Operation patterns.

(a) Experimental circuit.

(b) Single-phase equivalent circuit.

Fig. 5. Proposed circuit with resonance capacitor.

セラミックコンデンサなどを使用する。

また、共振回路の共振の鋭さQは(4)式で表される。(4)式より、Qは共振周波数と時定数で決定されることがわかる。Qが大きいほど、負荷電圧がより正弦波に近くなる。

$$Q = \frac{2\pi f_r L}{R} = 2\pi f_r \tau \tag{4}$$

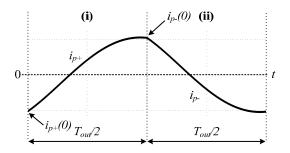

## 〈4・2〉回路方程式の導出

本論文では、トランス二次側に共振コンデンサを接続した直列共振回路について損失解析を行う。提案回路の損失解析を行う前に、提案回路の等価回路より、回路に流れる電流を定式化する。図 5 の等価回路より、回路方程式を導出することで、インバータ出力電圧が正の期間におけるトランス一次側電流  $i_{p+1}$ 、インバータ出力電圧が負の期間におけるトランス一次側電流  $i_p$ 、はそれぞれ(5)、(6)式で表すことができる。なお、 $v_{c+1}(0)$ および $v_{c-1}(0)$ は共振コンデンサ電圧の初期値である。

$$i_{p-} = Ce^{-\alpha t} \left\{ \begin{cases} \left\{ -\frac{V_{in}}{2} - v_{c-}(0) \right\} \left(\omega + \frac{\alpha^2}{\omega}\right) \\ -\alpha \frac{i_{p-}(0)}{\omega C} \\ + \frac{i_{p-}(0)}{C} \cos \omega t \end{cases} \right\} \sin \omega t \right\} \dots \dots (6)$$

$$\label{eq:constraints} \mathcal{L} \subset \mathcal{C}, \ C = n^2 C_r, \ \alpha = \frac{R}{2L} \ , \ \omega = \sqrt{\frac{1}{LC} - \alpha^2} \ \mathcal{C} \ \mathcal{B} \ \mathcal{S}.$$

(5), (6)式より,損失解析に必要なスイッチおよびトランスの電流実効値を計算することができる。

図 6 に(5), (6)式より計算したトランス一次側電流波形を示す。また、図 6 は共振周波数とスイッチング周波数が異なる場合の波形である。提案回路は出力周期の半周期ごとにいずれかの相が必ずスイッチングするため、出力周期中に2つの共振状態が存在し、トランス一次側電流は(5), (6)式の2式に支配される。なお、共振周波数とスイッチング周波数を等しくする場合は、図 6 の波形は正弦波となる。

## 5. 損失解析

ここでは、損失計算の容易な 1)出力周波数=共振周波数、 2)デッドタイムなし、という条件における損失計算式を示す。

トランス一次側に印加される電圧は $\pm V_{ii}/2$  の振幅を持つ 方形波であり、方形波の基本周波数の振幅は(7)式で表される。

$$V_{invout_{-}f} = \frac{4}{\pi} \frac{V_{in}}{2} = \frac{2V_{in}}{\pi} \dots (7)$$

特に、スイッチング周波数が共振周波数と等しい場合、インバータ側から見た回路インピーダンスは抵抗成分だけとなり、トランスには正弦波電流が流れる。このとき、各トランス一次側に流れる電流の最大値は(8)式となる。

Fig. 6. Primary current of the transformer.

$$I_{pm} = \frac{V_{invout\_f}}{\frac{R_{out}}{n^2}}$$

(8)

(8)式より、各トランス電流のピーク値はインバータの相数と無関係であることがわかる。

#### 〈5·1〉インバータ損失

多相インバータによる損失は、MOSFET のオン抵抗による導通損失、寄生ダイオードの順方向電圧による導通損失、スイッチング損失の3つに分類できる。しかし、MOSFET のスイッチング損失は、全領域でゼロ電流スイッチング (Zero Current switching: ZCS) が達成されるため、ゼロと仮定する。また、実際にはデッドタイム中に還流ダイオードに電流が流れ順方向電圧により損失が発生するが、流れる電流がオン抵抗に流れる電流に比べて小さく流れる期間も短いため、ここでは無視する。したがって、インバータの

MOSFET のオン抵抗に流れる電流を  $i_{DS}=I_{DSm}\sin \omega t=I_{pm}\sin(2\pi f_{sw}t)$ とすると、MOSFET のオン抵抗に流れる電流の実効値は(9)式で表される。

損失は MOSFET のオン抵抗による導通損失のみである。

$$I_{DSrms} = \frac{I_{DSm}}{\sqrt{2}} \tag{9}$$

ここで、提案回路の MOSFET のオン抵抗に流れる電流のデューティは D=0.5 であるため、素子 1 つ当たりの MOSFET 導通損失は(10)式で表される。

$$P_{cond\_mos} = I_{DSrms}^{2} R_{DS(on)} D = \frac{1}{4} I_{DSm}^{2} R_{DS(on)} \dots (10)$$

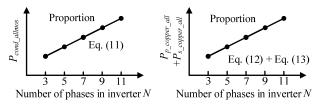

よって、全スイッチの導通損失の合計は(11)式で表される。

$$P_{cond\_allmos} = 2N \times \frac{1}{4} I_{DSm}^{2} R_{DS(on)} = \frac{N}{2} I_{DSm}^{2} R_{DS(on)} \dots \dots (11)$$

(11)式より、MOSFET の導通損失は相数に比例することがわかる。

#### 〈5・2〉トランスの銅損

トランスで発生する損失は、巻線抵抗による銅損とコアに発生する鉄損に分類できる。まず、銅損の計算方法を示す。トランスの一次側巻線に流れる電流は、(5)、(6)式で表されるため、トランス一次側銅損の合計は各トランス一次巻線の巻線抵抗  $R_{pwire}$  が全て等しいとすると (12)式で表される。

$$P_{p\_copper\_all} = N \times I_{prms}^2 R_{pwire} = \frac{N}{2} I_{pm}^2 R_{pwire} \dots (12)$$

なお、ここでは漏れインダクタンスに対して励磁インダクタンスが十分大きいものとして、励磁電流は無視している。また、トランス二次側銅損は、巻数比nおよび各トランス二次側巻線の巻線抵抗 $R_{swire}$ が全て等しいとすると(13)式で表される。

$$P_{s\_copper\_all} = \left(\frac{I_{prms}}{n}\right)^2 \times N \times R_{swire} = \frac{N}{2n^2} I_{pm}^2 R_{swire} \dots (13)$$

(12), (13)式より, トランスの銅損も相数に比例することが わかる。

#### 〈5·3〉トランスの鉄損

提案回路のトランスには方形波電圧,つまり高調波成分が含まれる電圧が印加される。したがって、コアメーカの提供する正弦波励磁時の鉄損データをそのまま利用することができない。そこで、コア材の鉄損に寄与するパラメータを測定し、非正弦波励磁下でもそのパラメータを補正することで鉄損を正確に推定する方法がある(14)が、実験環境の都合上、パラメータを測定することができない。今後、インバータ出力電力およびトランス二次側電力を実測し、その差分からさらに(12)式および(13)式で求めたトランスの銅損を差し引くことで鉄損 Power を求める予定である。

#### 〈5・4〉共振コンデンサ損失

本論文では、トランス二次側に共振コンデンサを接続する。共振コンデンサの損失は、コンデンサの等価直列抵抗 (ESR)とコンデンサに流れる電流から計算できる。共振コンデンサにはトランス二次側電流と同じ電流が流れるため、共振コンデンサの等価直列抵抗を  $R_c$  とすれば、共振コンデンサ損失は(14)式で表される。

$$P_{ESR} = \left(\frac{I_{pm}}{\sqrt{2}n}\right)^2 R_c = \frac{I_{pm}^2}{2n^2} R_c$$

(14)

したがって、提案回路の全導通損失  $P_{cond}$  は(11)~(14)式を用いて(15)式で表される。

$$P_{cond} = \frac{1}{2} \left[ N \left\{ R_{DS(on)} + R_{pwire} + \frac{R_{swire}}{n^2} \right\} + \frac{R_c}{n^2} \right] I_{pm}^{2} \dots (15)$$

以上をまとめると、提案回路の全損失は (16)式で表される。  $P_{loss} = P_{cond} + P_{core}$  .....(16)

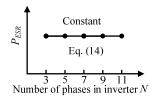

## 〈5·5〉インバータの相数に対する損失変化

図 7 に、インバータの相数を変化させた場合の各損失の傾向を示す。相数が変化することで、MOSFET のオン抵抗に流れる電流の周波数は(1)式にしたがって変化するが、(11)式に示すように電流実効値は変化しない。したがって、MOSFET の導通損失はインバータの相数に単純比例する。同様の理由で、マルチコアトランスの一次巻線および二次巻線による銅損も(12)、(13)式にしたがって、インバータの相数に比例する。また、共振コンデンサ損失はコンデンサ容量が変化しても ESR が変化しないとすれば(14)式にした

(a) Conduction loss of MOSFETs.

(c) Resonance capacitor loss.

Fig. 7. Power loss with regard to the number of phase in multi-phase inverter.

Table 2. Specification of the prototype circuit.

| Parameter                     | Symbol    | Rating               | Unit           |

|-------------------------------|-----------|----------------------|----------------|

| Output voltage                | $V_{out}$ | 100                  | V              |

| Primary number of turn        | $N_1$     | 5                    | turns          |

| Secondary number of turn      | $N_2$     | 10                   | turns          |

| Turn ratio                    | n         | 2                    |                |

| Switching frequency           | $f_{sw}$  | 500                  | kHz            |

| Output frequency              | $f_{out}$ | 2.5                  | MHz            |

| Duty cycle                    | D         | 0.5                  |                |

| Maximum flux density          | $B_m$     | 0.3                  | T              |

| Cross-sectional area of cores | S         | $112 \times 10^{-6}$ | m <sup>2</sup> |

がって相数に関係なく一定である。しかし実際は、共振コンデンサ損失は相数に応じて変化する。これは、共振に必要なコンデンサ容量に応じてESRが変化するためである。

なお、共振周波数がスイッチング周波数よりも低い場合もしくは高い場合は、トランス電流はトランス印加電圧よりも位相が遅れる、もしくは進む。この場合も、(5)、(6)式を用いてスイッチ、トランス電流の実効値を計算することで、損失を計算することが可能である。なお、この場合、スイッチング損失が発生するため、スイッチング損失の定式化が必要となる。

## 6. 実機検証

表 2 に回路の設計仕様を示す。負荷には MHz 帯でも無誘導の純抵抗負荷を用いる。また、5 相インバータには、MOSFET(RENESAS 製、H5N2508DL)を使用する。負荷に直列に共振用真空可変コンデンサ(明電舎製、SCV-151H55UW)を接続して、実験を行う。

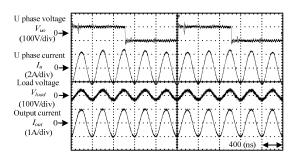

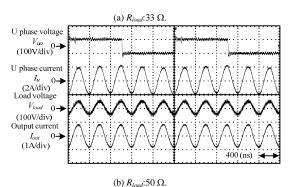

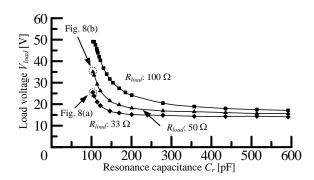

図 8(a), (b)に, LC 直列共振時の負荷抵抗  $33\Omega$ ,  $50\Omega$ における実験波形を示す。図 8(a), (b)より, LC 直列共振により負荷電圧がほぼ正弦波であることを確認できる。図 8(c)に,各負荷抵抗における共振コンデンサの値に対する負荷電圧の変化を示す。負荷電圧が最大となる共振点は共振コンデンサ  $C_r$ の値が 100 pF 以下の領域に存在するが,使用したコンデンサの耐圧が低いため  $C_r$ を 100 pF以上として実験した。

図 8(c)より、共振コンデンサ  $C_r$ を適切に設計することで負荷電圧を増加させることができ、高出力化を達成できることがわかる。

## 7. まとめ

本論文では、LC 直列共振回路を付加したマルチコアトランスと多相インバータを用いた MHz 級高周波電源のインバータの相数と発生損失の関係を明らかにするために損失の定式化を行った。

損失解析により、インバータの導通損失およびトランスの銅損がインバータの相数に比例することを明らかにした。また、共振コンデンサの損失は理論的にはインバータの相数に関係なく一定であることを確認した。以上により、損失解析をもとに提案回路の設計指針を把握することが可能であることを確認した。今後は、鉄損の正確な推定および実験による測定、ヒートシンクを含む提案回路の体積評価を予定している。

## 文 献

- (1) H. Ohguchi, R. Shimotaya, T. Shimizu, H. Takagi, M. Ito: "13.56MHz Current Source Inverter Based on Immittance Conversion Topology", T. IEEJapan, Vol. 121-D, No. 7, pp.805-813(2001)(in Japanese) 大口・下田屋・清水・高木・伊藤:「イミタンス変換理論を応用した 13.56MHz 電流出力形インバータ」, 電学論 D, Vol.121, No. 7, pp.805-813(2001)

- (2) H. Iwabuki, H. Iwata: "5kV/50A/2MHz High Voltage Inverter for Gas Discharge Laser without Step-up Transformer", T. IEEJapan, Vol. 127-D, No. 11, pp.1157-1163(2007)(in Japanese) 岩蕗・岩田:「放電レーザ用 5kV/50A/2MHz トランスレス高圧インバータの開発」, 電学論 D, Vol.127, No. 11, pp.1157-1163(2007)

- (3) D. Goodman, A. Bortkiewicz, G. Alley, and W. Holber, "RF Power Supply With Integrated Matching Network," U.S. Patent 6 887 339, Sep. 20 (2001)

- (4) H. Fujita, H. Akagi, S. Shinohara: "A 2-MHz 6-kVA Voltage-Source Inverter Using Low-Profile MOSFET Modules for Low-Temperature Plasma Generators", IEEE Transaction on Power Electronics, Vol.14, No.6, pp.1014-1020 (1999)

- (5) D. Puyal, C. Bermal, J. M. Burdio, J. Acero, I. Millan: "Versatile High-Frequency Inverter Module for Large-Signal Inductive Loads Characterization Up to 1.5 MHz and 7 kW", IEEE Transaction on Power Electronics, Vol.23, No.1, pp.75-87 (2008)

- (6) H. Ikeda, H. Yoshida, S. Shinohara: "Megasonic Transducer Drive Utilizing MOSFET DC-to-RF Inverter with Output Power of 600 W at 1 MHz", IEEE Transaction on Industrial Electronics, Vol.46, No.6, pp.1159-1173 (1999)

- (7) J. M. Rivas, O. Leitermann, H. Yehui, D. J. Perreault: "A Very High frequency DC-DC Converter Based on a class  $\Phi_2$  Resonant Inverter", IEEE Transaction on Power Electronics, Vol.26, No.10, pp.2980-2992 (2011)

- (8) M. P. Theodoridis, S. V. Mollov: "Robust MOSFET Driver for RF, Class-D Inverters", IEEE Transaction on Industrial Electronics, Vol.55, No.2, pp.731-740 (2008)

- (9) H. Nishiyama, K. Orikawa, S. Miyawaki, J. Itoh: "Consideration of a Frequency Amplify Power Converter Using a Neutral Voltage Fluctuation of a Square-wave Inverter and a Multiple Core Transformer", SPC-11-036 (2010) (in Japanese)

西山、折川、宮脇、伊東: 「方形波駆動時のインバータ中性点電位変動とマルチコアトランスを用いた周波数増幅電力変換器の一考察」, SPC-11-036 (2010)

- (10) J. Itoh, Y. Fujita, H. Nishiyama: "Frequency Multiplying Circuit Constructed from a Multi-phase Inverter and Multi-core Transformers",

(c) Load voltage related resonance capacitance.

Fig. 8. Experimental results with resonance capacitance.

ECCE Asia, pp. 807-813 (2012)

- (11) H. Maeoka, T.Noguchi: "Development of High-Voltage Pulse Power Supply Using Multiple Transformers with Novel Winding Structure", VT-05-7 (2004) (in Japanese)

- 前岡,野口:「新しい巻線方式に基づく多重トランスを用いた高電 圧パルス電源の開発」,VT-05-7 (2004)

- (12) G. Ortiz, J. Biela, D. Bortis and J. W. Kolar: "1 Megawatt, 20 kHz, Isolated, Bidirectional 12kV to 1.2kV DC-DC Converter for Renewable Energy Applications", The 2010 International Power Electronics Conference, pp. 3212-3219 (2010)

- (13) T. Yamaguchi, D. Azuma, H. Kifune, Y. Hatanaka: "A Novel Full-Bridge ZCS and ZVS High Frequency Power Supply with Phase Shift Control", SPC-02-095 (2002) (in Japanese) 山口,東,木船,畑中:「位相シフト制御フルブリッジ形高周波 ZVS-ZCS インバータ」, SPC-02-095 (2002)

- (14) M. Nakahara, K. Wada, T. Shimizu: "Discussion for analyzing iron loss into hysteresis- and eddy-current- loss in medium-frequency transformer for DC-DC converter", SPC-14-35/ MD-14-35 (2014) (in Japanese) 中原、和田、清水: 「DC-DC コンバータ用高周波変圧器の鉄損分離手法の検討」, SPC-14-35/ MD-14-35 (2014)