# 配線パターン設計に起因するインダクタンス特性に関する一考察

提橋 郁人・日下 佳祐・折川 幸司・伊東 淳一 (長岡技術科学大学)

### 1. はじめに

LSIの回路設計では、実際の回路に発生するノイズ、熱などを徹底的にシミュレーションにより検証し、開発工程およびコストの低減を目的としたフロントローディング技術が一般的に用いられる。近年、電力変換器の設計においてもこの技術が要求されており、特にプリント基板を用いた高周波電力変換器における諸特性の検証が重要となっている。

本論文では、電力変換器のサージ電圧やノイズに大き く寄与するプリント基板上のインダクタンスの特性につ いて、シミュレーションにより検討したので報告する。

## 2. 配線パターンのインダクタンス

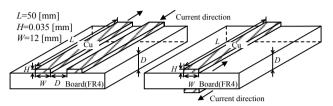

図1に検討する配線パターンのレイアウト図を示す。図 1(a)は基板の同平面上に平行にパターンを引き,図1(b)は基板の両面にパターンを引いたものとする。ここで,配線パターンはインバータのDCバスラインを想定し,パターン長Lは50 mm,銅箔の厚さHは35  $\mu$ m,パターン幅Wは12 mmとする。なお,インダクタンスを導出するにあたり,基板の材質および相互インダクタンスを考慮したインダクタンスの計算式は明らかにされていないため,Advanced Design System(Agilent社製)シミュレーションを用いて,各レイアウトのインダクタンスを算出する。

#### 3. シミュレーション結果

各レイアウトにおいて、基板上の2本のパターン間隔および基板の厚さDと、周波数fに対するインダクタンスの変化を検証するため、シミュレーションを行う。なお、シミュレーション結果から取得した反射係数 $\Gamma$ を用いて、(1)式よりインピーダンス $Z_{\rm in}$ を算出し $^{(1)}$ 、求めた $Z_{\rm in}$ を用いて(2)式よりインダクタンスを算出する。

$$\dot{Z}_{in} = \left(\frac{1+\Gamma}{1-\Gamma}\right) \times \dot{Z}_0 \tag{1}$$

$$L = \frac{\operatorname{Im}[\dot{Z}_{in}]}{2\pi f} \tag{2}$$

ここで、 $Z_0$ はシミュレーションの際に用いた特性インピーダンスである。また、(2)式は、自己インダクタンス $L_s$ と相互インダクタンスMを用いて、(3)式で表わされる(2)。  $L=2(L_s-M)$

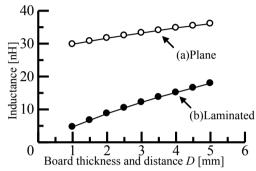

図2に各レイアウトにおけるパターン間隔および基板の厚さDを変化させたときのインダクタンスの変化を示す。図2より,両レイアウトにおいてDが大きくなるとインダクタンスが増加することがわかる。また,図1(b)のレイアウトは,図1(a)のレイアウトよりインダクタンスを小さくできる。これは,(3)より,配線パターンの自己インダクタンス $L_s$ は,両レイアウトで同じであるが,相互インダクタンスMが図1(b)は図1(a)と比較して大きいためである。

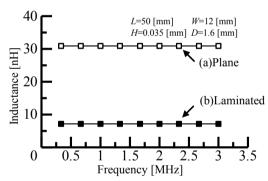

図3に周波数を変化させた場合の各レイアウトにおけるインダクタンスの変化を示す。インダクタンスは,図2

(a) Plane type (b) Laminated type Fig. 1. Layouts of wiring patterns.

Fig. 2. Characteristics of wiring pattern inductance in difference board thickness and distance.

Fig. 3. Frequency characteristic of wiring pattern

と同様に図1(b)のレイアウトの方が小さくできる。また、 配線パターンのインダクタンスは、3MHzまでの周波数 帯域では、配線パターンの寄生容量が小さく、インダク タンス成分が支配的であるためである。

図2,図3の結果から、配線パターンを両面に引き、パターンの間隔および基板の厚さを小さくすることで、配線インダクタンスを低減し、ノイズやサージ電圧の低減が可能であることがわかる。

今後は、プリント基板を製作しサージ電圧やノイズを 測定し、配線パターンのインダクタンスの違いによる影響を実機検証する予定である。

#### 文 献

- (1)市川古都美,市川裕一,CQ出版,「RFデザイン・シリーズ高周波 回路設計のためのSパラメータ詳解」

- (2)安藤, 和田:電学論 D, Vol132, No.4, pp.510-517(2011)「ブスバー配線の寄生インダクタンスを考慮した配線構造設計」