## 研究開発レター

# 3 レベルインバータの無負荷の損失の解析

学生員 樫原 有吾\* 正 員 伊東 淳一\*

## Power Loss Analysis of Three-level Inverter Topologies with No-load Loss

Yugo Kashihara\*, Student Member, Jun-ichi Itoh\*, Member

(20XX 年●月●日受付, 20XX 年●月●日再受付)

The present paper discusses the no-load loss of diode clump type, flying capacitor type and T-type three-level converter topologies. The no-load loss is calculated according to the operation of each three-level topology. The calculation results of no-load losses of the three-level topologies agree well with experimental results.

キーワード: 3 レベル電力変換器,連系インバータ,パラメータ設計,損失推定

Keywords: Three-level converter, Grid interconnection inverter, Parameter design, loss estimation

#### 1. はじめに

軽負荷時の運転時間が長い電力変換器では、軽負荷時の 損失算定が設計の上で重要である。軽負荷時には、電流に 依存しない損失、すなわち無負荷損失の影響が大きい<sup>(1)</sup>。こ れまで、3 レベルインバータのように複雑な回路について具 体的な無負荷損の導出法の検討は著者らの知る限りない。

本稿では、フィルタの小型化の観点から PV インバータなど連系インバータで注目を浴びている 3 レベルインバータで注目を浴びている 3 レベルインバータ(2)、(3)に発生する無負荷損失の計算方法を提案する。ここではダイオードクランプ(以下 DCLMP)、フライングキャパシタ(以下 FC)、T-type 中性点クランプ(以下 T-type NPC)の 3 つの回路の無負荷損失の発生メカニズムを明らかにし、計算値と実験結果を比較しよく一致したので報告する。

## 2. 回路トポロジーと無負荷損失の計算方法

電力変換器に発生する損失  $P_{Loss}$  は,(1)式で表せる。ここで, $P_1(i^2)$ は電流の2乗に比例する損失(導通損失), $P_2(i)$ は電流に比例する損失(スイッチング損失), $P_3$  は電流に依存しない損失(無負荷損失)である。

$$P_{Loss} = P_1(i^2) + P_2(i) + P_3$$

(1)

電圧がスイッチに印加されるとドレイン-ソース間の寄生容量に電荷が充電される。そして、オンのとき、寄生容量に蓄積された電荷がスイッチのオン抵抗で消費され、無負荷損失が発生する。従って、無負荷損失 P<sub>nloss</sub> は(2)式で導出

\* 長岡技術科学大学工学研究科

〒940-2188 新潟県長岡市上富岡町 1603-1 Graduate School of Engineering, Nagaoka University of

1603-1, Kamitomioka, Nagaoka Niigata, Japan 940-2188

できる。

$$P_{nloss} = \frac{1}{2} C_{ds} V_{sw}^{2} f_{c}$$

(2)

ここで、 $C_{ds}$  はドレイン-ソース間の寄生容量、 $V_{sw}$  は半導体素子の印加電圧、 $f_c$  はキャリア周波数である。また、ダイオードでも、同様に接合容量に蓄積された電荷がオンの時に内部抵抗で消費され、無負荷損失が発生する。

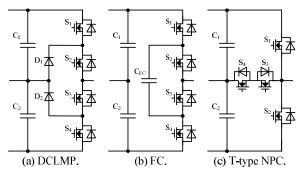

図 1 に、DCLMP、FC、T-type NPC の 3 つの 3 レベルトポロジーを示す $^{(2),(3)}$ 。以下、(2)式を元に、(3)つのトポロジーの無負荷損失について発生メカニズムと共に考察する。

<2.1>DCLMP いろいろな変調方式があるが、いま、図1(a)において、出力電圧指令値の半周期の期間毎に $S_1$ と $S_3$ 、 $S_2$ と $S_4$ がそれぞれ1対となり、出力電圧の極性に応じて、1対の素子がキャリア周波数で、もう1対の素子が出力周波数でスイッチングを行うとする。 $S_1$ 、 $S_3$ がキャリア周波数でスイッチングしている期間、 $S_2$ 、 $S_4$ は出力周波数でスイッチングするため、この期間は $S_2$ 、 $S_4$ に無負荷損失は発生しない。一方、 $D_1$ は $S_2$ 、 $S_4$ に, $D_2$ は $S_1$ 、 $S_3$ に伴い、キャリア周波数でスイッチングするときに、無負荷損失が発生する。

Fig. 1. Single leg three-level converter topologies (Single-phase).

なお、 $S_1$ 、 $S_3$ 、 $D_2$  と  $S_2$ 、 $S_4$ 、 $D_1$  は出力周波数の正負に伴い、 半周期毎にスイッチングする。また、この回路では、中性 点電位でクランプされるため、スイッチの印加電圧は直流 電圧の 1/2 となる。従って、DLCMP に発生する無負荷損失  $P_{plass 3D}$  は、(3)式で得られる。

$$P_{nloss_{3D}} = 2\left\{\frac{1}{2}C_{ds}\left(\frac{V_{dc}}{2}\right)^{2}\frac{f_{c}}{2}\right\} + 2\left\{\frac{1}{2}C_{j}\left(\frac{V_{dc}}{2}\right)^{2}\frac{f_{c}}{2}\right\} = \frac{1}{2}\left(C_{ds} + C_{j}\left(\frac{V_{dc}}{2}\right)^{2}f_{c}\right)$$

(3)

ここで、 $C_f$ はダイオードの接合容量、 $V_{cc}$ は直流電圧である。 <2.2>FC ここで考える変調方式は、図 1(b)において、 $S_1 \geq S_4$ 、 $S_2 \geq S_3$ のそれぞれ相補動作する素子を、出力電圧指令値 1 周期の期間、常にキャリア周波数でスイッチングを行うとする。また、各素子の印加電圧は直流電圧の 1/2 となる。相補動作となる素子において、スイッチの印加電圧は出力電圧指令値周期の半周期ごとにフライングキャパシタによって常に片方のスイッチのオンオフするタイミングで変化する。従って、一方のスイッチは印加電圧ゼロでオンするため無負荷損失は発生しない。すなわち、無負荷損失は全てのスイッチにおいて出力電圧指令値の半周期の期間のみ発生し、FC に発生する無負荷損失は(4)式となる

$$P_{nloss\_3F} = 4 \left\{ \frac{1}{2} C_{ds} \left( \frac{V_{dc}}{2} \right)^2 \frac{f_c}{2} \right\} = C_{ds} \left( \frac{V_{dc}}{2} \right)^2 f_c$$

(4)

<2.3>T-type NPC 図 1(c)おいて出力電圧指令値が正の時、 $S_1 \geq S_3$ 、 $S_4$ が、指令値が負の時、 $S_2 \geq S_3$ 、 $S_4$ がキャリア周波数でスイッチングする。ここで、T-type NPC の各素子の耐圧は、他のトポロジーと異なり、 $S_1 \geq S_2$ は直流電圧、 $S_3 \geq S_4$ は直流電圧の 1/2 となる。しかし、 $S_1$ から  $S_2$ へ転流する際、必ず  $S_3$ 、 $S_4$ を経由してスイッチングするので、 $S_1$ 、 $S_2$ のスイッチング電圧は直流電圧の 1/2 となる。また、DCLMP と同じく、スイッチングする素子は出力周波数の正負で入れ替わる。さらに、 $S_1$ 、 $S_2$ は、転流の際に印加電圧が直流電圧から直流電圧の 1/2 に変化する際にも無負荷損失が発生する。よって、T-type NPC に発生する無負荷損失は(5)式で得られ、フライングキャパシタ形と同じ式となる。

$$P_{nloss\_3T} = 2\left\{\frac{1}{2}C_{ds}\left(\frac{V_{dc}}{2}\right)^{2}\frac{f_{c}}{2}\right\} + 2\left\{\frac{1}{2}C_{ds}\left(V_{dc} - \frac{V_{dc}}{2}\right)^{2}\frac{f_{c}}{2}\right\} = C_{ds}\left(\frac{V_{dc}}{2}\right)^{2}f_{c}$$

(5)

#### 3. 実験検証

検討した無負荷損失の妥当性を確認するために、3つの3レベルトポロジーを試作し、軽負荷時の損失について評価する。定格出力を3.3kWとして、DCLMPとFCは300V耐圧の素子を、T-type NPCは600V耐圧の素子を選定した。ここで、スイッチング素子の寄生容量は10個の試料を用いてLCRメータ(5 V, 10 kHz)で測定しその平均値とした。また、FCのフライングキャパシタのESRも5個の試料を用いて同様に測定しその平均値とした。ここで、寄生容量やESRは1試料の測定だけでは、測定結果に大きな誤差を含む可能性があるため、注意が必要である。

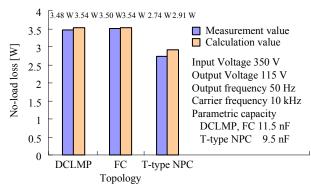

図2に3レベルトポロジーに発生する無負荷損失につい

Fig. 2.No-load loss comparison of the three-level inverters.

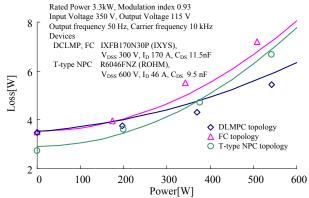

Fig. 3. Power loss of the three-level inverters.

て計算式と比較した結果を示す。それぞれのトポロジーにおいて、実験値と計算値の誤差が DCLMP トポロジーは1.7%, FCトポロジーは1.1%, T-type NPCトポロジーは5.9%で一致し、無負荷損失の計算式の妥当性を確認した。

図3に負荷を無負荷から550Wまで変化させたときの損失特性を示す<sup>(4)</sup>。図3よりDCLMPトポロジーは最大誤差7%以下,FCトポロジーは最大誤差8%以下,T-type NPCトポロジーは最大誤差6%以下で一致した。

## 4. 結論

本論文では、3つの3レベルインバータの無負荷損失の発生メカニズムを考察した。そして、試作機を作成し、軽負荷時の損失について実験値と計算値を比較した。その結果、誤差が6%以内の誤差でよく一致し、提案する無負荷損失の計算方式が妥当であることを確認した。

### 文 献

- (1) 日向敏文, 伊東淳一:「インダイレクトマトリックスコンバータの無 負荷運転時における損失の一考察」, 平成 22 年度北陸支部連合大会, A-75 (2010)

- (2) A. Nabae, I. Takahashi, H. Akagi, "A new neutral-point-clamped PWM inverter", IEEE Trans.Industry Applications, Vol.IA-17, 1981, pp.518-523.

- (3) F. Z. Peng: "A Generalized Multilevel Inverter Topology with Self Voltage Balancing", IEEE Transactions on industry applications, Vol.37, No.2, pp. 2024-2031 (2001)

- (4) Yugo Kashihara, Jun-ichi Itoh, "The performance of the multilevel converter topologies for PV inverter", International Conference on Integrated Power Electronics Systems (CIPS) 2012, Nuremberg, Germany (2012)