## 小型連系インダクタを有する三相系統連系インバータの FRT 制御

## 永井 悟司\* 伊東 淳一(長岡技術科学大学)

FRT Capability of Three-phase Grid-tied Inverter with Minimized Inductor

Satoshi Nagai\*, Jun-ichi Itoh (Nagaoka University of Technology)

This paper proposes a Fault Ride-through (FRT) control method for a three-phase grid-tied inverter with a minimized inductor. The grid-tied inverter is required to satisfy the FRT requirements. The proposed FRT control method suppresses the output inverter current overshoot with the minimized inductor applying a high-gain disturbance observer and a high-speed operation which outputs reverse voltage for the output current vector at the grid fault. The grid-tied inverter with the minimized inductor satisfies the FRT requirements with the proposed FRT control method. As the experimental results, the maximum overshoot of the output inverter current with the inductor of 0.48 mH (%Z = 0.38%) is reduced by 58.3% with the proposed FRT operation.

キーワード: 三相系統連系インバータ、FRT、小型連系インダクタ、カウンタ電圧

(Three-phase grid-tied inverter, FRT, minimized inductor, counter voltage)

#### 1. はじめに

近年、省エネルギーの観点から分散電源システムである太陽光発電、風力発電、燃料電池システムが活発に研究されている。分散電源システムにおいて、系統へ電力を供給するためにパワーコンディショニングシステム(以下、PCS)が用いられる。PCS は小型化の要求が強く、特にシステム内で大きな体積割合を占めている連系インダクタの小型化が求められている(1)(2)。連系インダクタの小型化の手法として、次世代スイッチング素子(e.g. SiC-MOSFET、GaN-FET)を適用したインバータの高周波化がある。高周波化により、出力電流のスイッチングリプルの観点からインダクタンスを低減し、連系インダクタの小型化ができる。しかし、連系インダクタンスの低減によりインダクタ電流制御器の外乱抑圧性能が低下し、インダクタ電流 THD (Total Harmonic Distortion)が増加する問題がある(3)。

一方、PCS は系統に瞬時電圧低下(以下、瞬低)が発生しても PCS が系統から解列することなく運転を継続することが求められている(Fault Ride-through: FRT)(4)-(8)。これにより、瞬低復帰後においても系統の電力需給のバランスが崩れないため系統電力の安定性を確保できることから、瞬低発生時の大規模停電などの問題を回避できる。また、日本のJEAC9701 による FRT 要件において系統電圧復帰時の出力電流オーバーシュートを定格電流に対して 150%以下に抑制することが求められている(8)。加えて、ドイツの E.ON コードでは残電圧 0%の瞬低においてもインバータの運転継

続が求められている(5)。しかし、低インダクタンスの PCS では瞬低発生時または復帰時に外乱抑圧性能低下に起因し たインダクタ電流オーバーシュートが発生する。これによ り、インダクタ電流が PCS の出力電流に対する電流閾値を 超過してインバータが解列するため、FRT 要件を満足でき ない。これまでに、FRT 制御法として瞬低時に直流中間電 圧を制御する手法(6)や電圧振幅と出力電力制御を適用した 手法(7)が提案されてきている。しかし、上記制御手法では瞬 低の高速検出または瞬時に出力電流オーバーシュート低減 を行うためのインバータ出力制御を考慮した FRT 制御法で はないため低インダクタンスの三相系統連系インバータで は出力電流オーバーシュートの発生が懸念される。これに 対して、著者らはこれまでに、小型連系インダクタを有す る単相系統連系インバータにおいて高速ゲート遮断と高速 外乱オブザーバ(DOB) $^{(3), (9)-(11)}$ を併用したインバータ出力電 流オーバーシュート抑制手法を提案し、また、FRT 要件を 満足する連系インダクタの設計指針を示している(12)。しか し、FRT 動作を考慮した低インダクタンスを有する三相系 統連系インバータついては検討していない。PCS は三相交 流へ連系するケースも多いため、分散電源システムの FRT 要件対応を考慮すると, 三相系統連系における検討も重要 である。また, 三相インバータでは各相電流のオーバーシ ュート抑制を考慮しなければいけないため、瞬時に出力電 流に対するインバータの出力電圧ベクトル操作が必要とな る。

本論文では、低い連系インダクタンスを有する三相系統

連系インバータに対して負荷電流を急激に減少させる瞬時カウンタ電圧出力動作と高速DOBを適用したFRT制御法を提案する。瞬時カウンタ電圧出力は瞬低発生時または復帰時にインバータ出力電流ベクトルに対して逆方向の電圧ベクトルを出力することで実現する。また、インバータ出力電流に対して逆方向の電圧ベクトルを出力するためにゲート遮断を適用する。実験結果より提案FRT制御法を用いることで従来FRT制御法と比較して瞬低時のインダクタ電流オーバーシュート量を58.3%改善し、低インダクタンスを有する三相系統連系インバータにおいてFRT要件を満足できることを確認したため報告する。

# 2. 低インダクタンスによる電流制御器構成時の課題

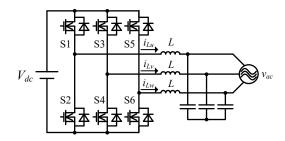

図 1 に三相系統連系インバータの回路図を示す。本論文では、基礎検討として 2 レベルインバータにおける連系インダクタ L の低インダクタンス化を検討する。まず、インバータの電流制御器を PI 制御器で構成するとき、電流制御器の外乱伝達関数  $G_{dis}(s)$ は(1)式で示される。

$$G_{dis}(s) = \frac{1}{L} \frac{s}{s^2 + 2\zeta \omega_{acr} s + \omega_{acr}^2}$$

(1)

ここで、 $\zeta$ は制動係数、 $\omega_{acr}$  は PI 制御器の固有角周波数、s はラプラス演算子である。(1)式より、連系インダクタンスが低下するほどに外乱ゲインが増加することがわかる。

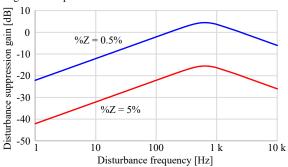

図2に出力電力1kWにおける電流制御器の外乱抑圧特性を示す。図2より、パーセントインピーダンスを0.5%に設計した場合では5%時と比較して外乱ゲインが高くなり、外乱抑圧性能が低下することがわかる。これにより、低インダクタンス時では外乱の影響を受けやすくなるためインバータ出力電流にひずみが発生する。また、インダクタ電流のdi/dtはインダクタンスに反比例するため、系統電圧の瞬低発生時や復帰時などの過渡動作時にインダクタ電圧が変化することで、インダクタ電流に過大なオーバーシュートが発生してしまう。

## 3. 高速カウンタ電圧出力動作と高速外乱オブザ ーバを併用した FRT 制御法

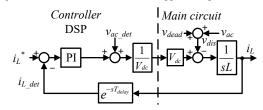

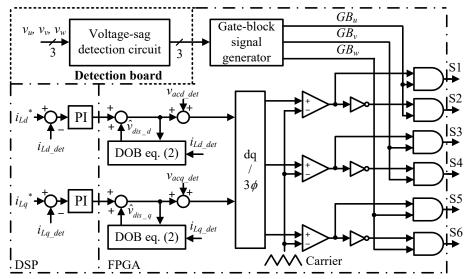

〈3・1〉従来 FRT 制御法 図 3 に従来用いられる系統連系インバータの電流制御器のブロック線図を示す。ここで, $i\iota^*$ は連系インダクタ電流指令値, $i\iota$  は連系インダクタ電流抗い値。 $i\iota$  は連系インダクタ電流検出値,PI は PI 制御器,vac は系統電圧,vac は系統電圧検出値,vdead はデッドタイム誤差電圧,Tdetay は検出遅延時間である。電流制御器を Digital Signal Processor (DSP)へ実装し,系統電圧のフィードフォワード補償を行うことで系統連系を実現する。また,ベクトル制御により dq 軸上で電流制御を行い,系統電圧の瞬低を検出した際に 1.0p.u.の無効電流注入を行うことで FRT 制御を実現する。しかし,従来 FRT 制御は DSP などの低速なコントローラで実装されるため,連系インダクタを低インダクタンス化した場合,瞬低などの過渡動作に対して検出遅延やサ

Fig. 1. Three-phase inverter circuit with LC filter.

Fig. 2. Characteristics of disturbance suppression performance.

Fig. 3. Control block diagram of conventional method.

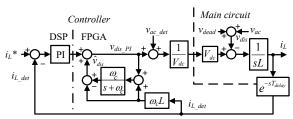

Fig. 4. Control block diagram of conventional method with high-gain DOB.

ンプリング遅延の影響を無視できず、出力電流に過大なオーバーシュートが発生する。加えて、定常動作においてデッドタイム誤差電圧やスイッチング素子のオン電圧によるインバータ出力電圧誤差が生じる。これらの外乱により、インダクタ電流 THD が増加する。したがって、低インダクタンス時に FRT 要件を満足させるためにはこうした外乱要素を補償可能な高速応答を有する制御が必要となる。

図4に従来の電流制御器に対して高速 DOB を適用したブロック線図を示す。DOB による外乱補償電圧 は(2)式で示される。

$$\hat{v}_{dis} = \frac{\omega_c}{s + \omega} \left( v_{dis\_PI} + \omega_c Li_{L\_det} \right) - \omega_c Li_{L\_det}$$

(2)

ここで、 $\omega$ は DOB のカットオフ角周波数、 $v_{dis\_PI}$ は PI 制御器の出力と DOB による補償値の和である。目標値応答は電源周波数に応答すればよいので、DSP により低速に制御する。また、DOB を高速制御が可能な Field Programmable Gate

Fig. 5. Control block diagram of proposed FRT operation with high-speed counter voltage output operation.

Array (FPGA)へ実装することにより高速サンプリングを実現し、広帯域な外乱補償を可能とする。さらに、系統電圧の補償に関しては DOB で補償すると DOB 内のローパスフィルタ(以下、LPF)により補償に遅延が発生するため FPGA内で高速にサンプリングしフィードフォワード補償を行う。これによりデッドタイム誤差電圧やスイッチング素子のオン電圧によるインバータ出力電圧誤差が補償できる。しかし、図 4 の制御器においても検出遅延やサンプリング遅延が発生するため、瞬低時では低インダクタンスによりインダクタ電流のオーバーシュートが発生する。特に、残電圧 0%の瞬低においてインダクタ電流オーバーシュートが最大となり、FRT 要件の満足が困難となる。

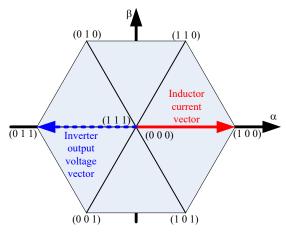

⟨3・2⟩ 提案 FRT 制御法 図 5 に高速カウンタ電圧出力動作と高速 DOB を併用した FRT 制御法,図 6 に瞬低時のカウンタ電圧出力のベクトル図の概要を示す。カウンタ電圧出力は瞬低発生時または復帰時の出力電流ベクトルに対して逆ベクトルのインバータ電圧を出 力することにより実現する。ここで、図 6 の各基本電圧ベクトルは、三相インバータにおける 3 つのレグのスイッチング関数(s1 s2 s3)により表現される。

$$s_{x} = \begin{cases} 1 \text{ (S}_{2x-1}: \text{ON, S}_{2x}: \text{OFF}) \\ 0 \text{ (S}_{2x-1}: \text{OFF, S}_{2x}: \text{ON)} \end{cases} (x = 1, 2, 3) \dots (3)$$

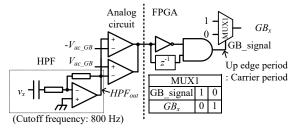

また、カウンタ電圧を出力する方法として、本論文ではゲート遮断動作を適用する。さらに、高速カウンタ電圧出力動作はアナログ回路によって系統電圧の瞬低または復帰を検出した際に信号を出力する回路を構成し、この回路から出力される信号を基に FPGA により瞬時にゲート遮断を行う。また、カウンタ電圧出力期間はキャリア周期と同様にすることでカウンタ電圧出力後も電流が連続的に流れるように設定する。以上から、アナログ回路と FPGA を適用することで遅延時間を低減したカウンタ電圧の出力が可能である。

Fig. 6. Space vector for inductor current and inverter output voltage at voltage sag.

Fig. 7. Voltage sag detection circuit and gate-block signal generator.

図 7 に瞬低検出回路とゲート遮断信号生成器の構成について示す。ここで、 $v_x$ は各相電圧(x=u,v,w)、 $V_{ac\_GB}$ はゲート遮断閾値、 $GB_x$ は各レグのゲート遮断信号(x=u,v,w)である。瞬低検出回路はハイパスフィルタ(以下、HPF)で構成し、HPF の微分の特性を利用して瞬低検出を行う。HPF のカットオフ周波数を系統電圧の基本波周波数に対して十分高くすることで、瞬低などの過渡的な動作が発生した際に HPFの出力がオーバーシュートする特性を適用する。HPF の出力  $HPF_{out}$ とゲート遮断閾値  $V_{ac\_GB}$  を比較することで瞬低検出信号を生成する。瞬低検出信号を基に FPGA 内でエッジを生成する。このエッジをキャリア周期と同等としダウン

Fig. 8. Inductor average current detection method for low inductance.

Table I. Experimental condition.

| Output power   | $P_{out}$  | 1 kW            | Carrier fre.        | $f_{cry}$   | 100 kHz    |

|----------------|------------|-----------------|---------------------|-------------|------------|

| DC link vol.   | $V_{dc}$   | 400 V           | Samp. fre. of $i_L$ |             | 400 kHz    |

| Grid voltage   | $v_{ac}$   | $200 \ V_{rms}$ | Ang. fre. of ACR    | $\omega_n$  | 4000 rad/s |

| (line to line) |            |                 |                     | $f_{samp}$  | 20 kHz     |

| Inter. Induc.  | L          |                 | Samp. fre. of DOB   | $f_{so}$    | 100 kHz    |

| (%Z)           |            | (0.38%)         | Cutoff fre. of DOB  | $f_c$       | 2 kHz      |

| Dead time      | $t_{dead}$ | 0.5 μs          | GB delay time       | $t_{delay}$ | < 6 µs     |

エッジとする。このダウンエッジを PWM 出力の AND 回路 へ入力することでゲート遮断を実行できる。また、瞬低検 出回路とゲート遮断信号生成器は各相電圧  $v_u$ ,  $v_v$ ,  $v_w$ に対して接続する。

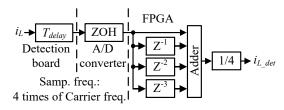

〈3・3〉低インダクタンス時の電流検出法 パルス幅変調(PWM)などでインバータを駆動する場合、インダクタ電流検出値を三角波キャリアのピークで検出することでインダクタ電流平均値を検出する。しかし、連系インダクタンスが低く検出遅延時間を有する場合、インダクタ電流のスイッチングリプルが大きくなることが原因で、インダクタ電流検出点が平均値検出点からずれる。これにより、瞬時値の平均電流検出が不可となり、インダクタ電流制御が指令値に追従することが不可となる。

上記問題を解消する手法として、図 8 にインダクタ電流 平均検出法を示す。キャリア周波数に対して検出点をキャリアピーク、ボトム、ピークとボトムの中点である計 4 点で検出することで電流検出のサンプリング周波数をキャリア周波数の 4 倍とする。キャリア周期内に検出した 4 点の電流検出値を合算し、取得した 4 点の電流平均値を算出することで低インダクタンスでも電流平均値取得が可能である。本論文では、この電流検出法を適用する。

#### 4. FRT 要件を満たす最小連系インダクタンス

FRT 要件を満たすためには系統電圧復帰時の出力電流オーバーシュートを150%以下へ抑制する必要があるため、インバータ出力電圧と系統電圧に対して連系インダクタンスが接続されたモデルで解析を行う。また、三相を単相に分解して検討することができるので文献(12)と同様にFRT 要件を満たすインダクタンスを以下の式により導出できる。

$$L = \frac{V_{ac}}{I_{I_{ab}} - I_{I}} t_{bd} \tag{4}$$

ここで、 $V_{ac}$ は系統電圧ピーク値、 $t_{bd}$ は瞬低発生からカウンタ電圧が出力されるまでの遅延時間、 $I_{L,th}$ は FRT 要件を満たすインダクタ電流の最大値、 $I_L$ は定常動作の定格出力電流ピーク値である。

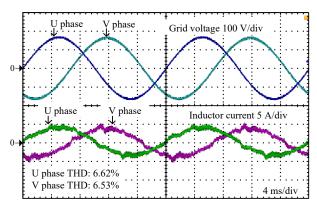

(a) Conventional FRT control with dead-time compensation.

(b) Proposed FRT control with high-gain DOB. Fig. 9 Steady state operation without voltage sag.

### 5. 実験結果

本論文ではインダクタ電流オーバーシュートの観点から 最悪条件となる残電圧 0%の瞬低での運転継続(ZVRT: Zero-voltage Ride-through)について検証を行う。また、外乱の変動が最大となるように、U 相系統電圧のピークで瞬低または復帰が発生する条件で実験を行う。表 1 に ZVRT の実験条件を示す。今回は 1 kW の連系インバータに対して定格運転における ZVRT 動作検証を行う。また、カウンタ電圧出力遅延時間を 6  $\mu$ s 未満とすると連系インダクタンスは(4)式より 0.48 mH (%Z = 0.38%)となる。この算出したインダクタンスにおいて実機検証を行う。

図9に従来FRT制御法と提案FRT制御法を適用した場合の定常動作の実験結果を示す。図9(a)より、従来デッドタイム誤差補償を適用したインダクタ電流制御では低インダクタンス化による外乱抑圧性能の低下によって、デッドタイム誤差電圧など電流制御器に対する外乱によりインダクタ電流にひずみが発生する。従来デッドタイム誤差補償適用時のインダクタ電流THDはU相電流:6.62%、V相電流:6.53%であることを確認した。系統連系インバータでは系統連系規定(4)により出力電流THDを5%以下に抑制することが要求されている。したがって、従来デッドタイム誤差補償では規定を満足できない。一方、図9(b)より、従来デッドタイム誤差補償と比較して、高速DOBを適用した場合は定常動作時のインダクタ電流THDを大きく改善できている

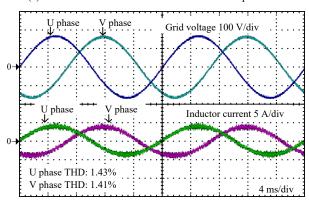

(a) Conventional FRT control.

(b) Conventional FRT control with high-gain DOB.

(c) Proposed FRT control.

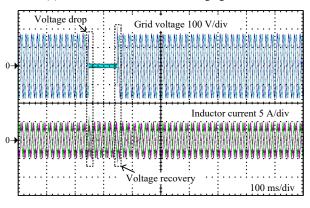

Fig. 10. Experimental results of short grid failure.

ことがわかる。これは、連系インダクタンスが低くなっても、高速 DOB により電流制御器の外乱抑圧性能が向上するためである。また、このときのインダクタ電流 THD は U 相電流: 1.43%、V 相電流: 1.41%であることを確認した。したがって、系統連系規定によるインダクタ電流 THD 5%以下を満足できることを確認し、高速 DOB を適用することでインダクタ電流 THD を 78.4%改善した。

図 10 に各制御法を適用した ZVRT 動作の実験結果を示す。図 10 (a)より従来 FRT 制御適用時では瞬低発生時にインダクタ電流オーバーシュートが発生し、過電流閾値を超過することでインバータ出力が停止することがわかる。しかし、図 10 (b), (c)のように従来 FRT 制御への高速 DOB 適用時または提案 FRT 制御法適用時にはインダクタ電流オーバ

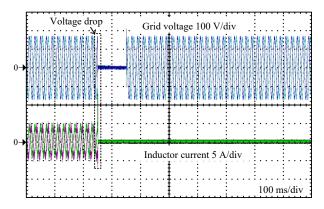

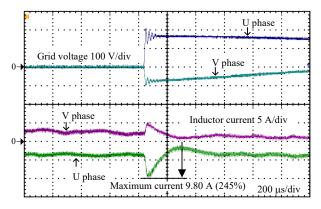

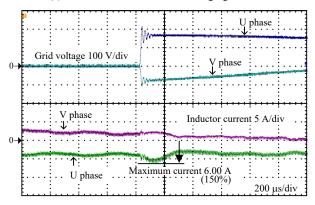

(a) Conventional FRT control.

(b) Conventional FRT control with high-gain DOB.

(c) Proposed FRT control.

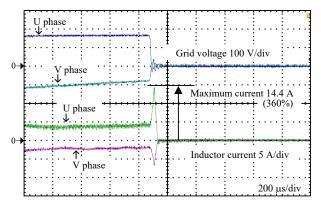

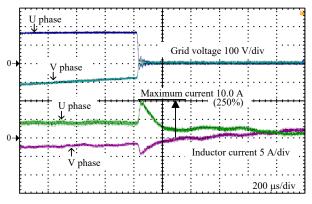

Fig. 11. Experimental results of FRT operation at voltage drop.

ーシュートを過電流閾値以下に抑制しインバータの運転継 続が可能であることが確認できた。

図 11 に各制御法を適用した ZVRT 動作における瞬低発生時の実験波形を示す。従来 FRT 制御を適用した図 11 (a)では 14.4 A (360%)のインダクタ電流オーバーシュートが発生した。これは、DSP の制御周期が 20 kHz であることと、電圧や電流検出遅延により出力電流制御に遅延が発生することで過渡的な外乱の補償が不可となるためである。これにより、低い連系インダクタンスを適用しているため電流変化量が増加することから検出遅延や制御遅れによってインダクタ電流のオーバーシュートが発生する。瞬低発生時のインダクタ電流オーバーシュートを抑制するためには高速な外乱補償が必要である。図 11 (b)の従来 FRT 制御に高速 DOB

を適用した実験結果では、図 11 (a)と比較して瞬低時のインダクタ電流オーバーシュートを抑制できている。これは、FPGA に実装した DOB により高速に外乱を補償できるため、瞬低などの瞬時的な外乱の補償もできるためである。このときのインダクタ電流オーバーシュート量は 10.0 A (250%)であった。一方、図 11 (c)の提案 FRT 制御適用時では、インダクタ電流オーバーシュートを 6.48 A (162%)に抑制できることを確認した。提案法では高速 DOB に加えて、高速に瞬低を検出した後、瞬時にカウンタ電圧を出力するため図 11 (b)以上にオーバーシュートを抑制できている。

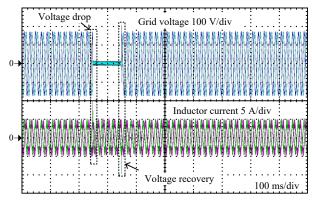

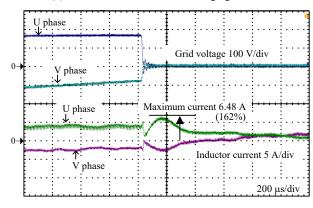

図 12 に各制御法を適用した ZVRT 動作における瞬低から 復帰した瞬間の実験波形を示す。従来 FRT 制御法へ高速 DOB を適用した図 12 (a)では、9.80 A (245%)のインダクタ電 流オーバーシュートが発生する。FRT 要件により系統復帰 時にはオーバーシュートを定格電流ピークに対して 150% 以下に抑制する必要がある。以上から、高速 DOB を適用し た従来 FRT 制御法ではオーバーシュートの抑制が不十分で あることがわかる。図 12 (b)に提案 FRT 制御法における実験 結果を示す。提案法を用いることで図 12(a)と比較してイン ダクタ電流オーバーシュートを抑制できることがわかる。 ここで、インダクタ電流オーバーシュートは 6.00 A (150%) となることを確認し、FRT 要件を満たした ZVRT 動作が可 能であり提案 FRT 制御の有用性が確認できた。以上から、 提案法を用いることで連系インダクタンスを低減でき, JEAC9701 の FRT 要件による瞬低復帰時のインダクタ電流 オーバーシュート量の規定を満たし、E.ON コードに定めら れる ZVRT 動作の両方を満たす FRT 動作が確認できた。

## 5. まとめ

本論文では、三相系統連系インバータに対して高速 DOB と高速カウンタ電圧出力動作を併用した FRT 制御を提案した。提案法により連系インダクタンスを%Z = 0.38%に低減した三相系統連系インバータにおいて解列することなく ZVRT 動作を実現し、瞬低復帰時のインダクタ電流オーバーシュート量を 150%以下へ抑制できることを確認した。よって、従来 FRT 制御法と比較して、瞬低時のインダクタ電流オーバーシュート量を 360%から 150%へ低減し、インダクタ電流オーバーシュート量を 58.3%改善できた。以上から、提案法の適用により連系インダクタンスの低減が可能であることを確認した。今後の課題は、更なるインダクタ電流オーバーシュート抑制法を検討し、三相瞬低以外に 1 相または 2 相瞬低動作の検証を行う。

#### 文 献

- (1) R. Peña-Alzola and M. Liserre,"LCL-Filter Design for Robust Active Damping in Grid-Connected Converters," *IEEE Trans. Ind. Info.*, Vol. 10, No. 4, 2014, pp. 2192-2203.

- (2) R. Beres, X. Wang, F. Blaabjerg, M. Liserre, C. Bak, "A Review of Passive Power Filters for Three-Phase Grid Connected Voltage-Source Converters" *IEEE Journal Emerging and Selected Topics in Power Electron.*, 2015.

- (3) S. Nagai, H. N. Le, T. Nagano, K. Orikawa, J. Itoh, "Minimization of

(a) Conventional FRT control with high-gain DOB.

(b) Proposed FRT control.

Fig. 12. Experimental results of FRT operation at voltage recovery.

Interconnected Inductor for Single-Phase Inverter with High-Performance Disturbance Observer", *IEEE International Power Electron. Motion Control Conf. - ECCE Asia*, No. Wb8- 06, 2016.

- (4) 系統連系専門部会編:「系統連系規程 JEAC9701-2012」, 日本電気協会 (2013)

- (5) M. Tsili, S. Papathanassiou, "A review of grid code technical requirements for wind farms", IET Renew. Power Gener., Vol. 3, No. 3, pp. 308-332, 2009.

- (6) Guangqian Ding, Feng Gao, Hao Tian, Cong Ma, Mengxing Chen, Guoqing He, and Yingliang Liu, "Adaptive DC-Link Voltage Control of Two-Stage Photovoltaic Inverter During Low Voltage Ride-Through Operation", *IEEE Trans. Power Electron.*, Vol. 31, No. 6, pp. 4182-4194, 2016.

- (7) Jaber Alipoor, Yushi Miura, and Toshifumi Ise, "Voltage Sag Ride-through Performance of Virtual Synchronous Generator", *IEEJ J. Ind. Appl.*, Vol. 4, No. 5, pp. 654-666, 2015.

- (8) RPI-M20A, Delta Electronics, Inc., Taipei, Taiwan, 2014. [Online]. Available: http://www.deltaww.com/fileCenter/Products/Download/05/05 01/RPI-M20A\_TechData\_20141126.pdf

- (9) K. Lee, T. M. Jahns, T. A. Lipo, V. Blasko and R. D. Lorenz, "Observer-Based Control Methods for Combined Source-Voltage Harmonics and Unbalance Disturbances in PWM Voltage-Source Converters" *IEEE Trans. Ind. Appl.*, Vol. 45, No. 6, 2009, pp. 2010-2021.

- (10) N. Hoffmann, M. Hempel, M. C. Harke and F. W. Fuchs, "Observer-based Grid Voltage Disturbance Rejection for Grid Connected Voltage Source PWM Converters with Line Side LCL filters" *IEEE Energy Conversion Congress and Expo. (ECCE)*, 2012, pp. 69-76.

- (11) T. Hoshino, J. Itoh, and T. Kaneko, "Dead-time Voltage Error Correction with Parallel Disturbance Observers for High Performance V/f Control" IEEE Ind. Appl. Conf., 2007. 42nd IAS Annual Meeting, pp. 2038-2044.

- (12) S. Nagai, K. Kusaka, J. Itoh, "FRT Capability of Single-phase Grid-connected Inverter with Minimized Interconnected Inductor", in Proc. IEEE Appl. Power Electron. Conf. and Expo. (APEC) 2017, No. 1800, pp. 2802-2809, 2017.