# Thermal Stress Reduction for DC-link Capacitors of Three-phase VSI with Multiple PWM Switching Patterns

Koroku Nishizawa Nagaoka University of Technology Nagaoka, Niigata, Japan koroku\_nishizawa@stn.nagaokaut.ac.jp

> Akihiro Odaka Fuji Electric Co., Ltd. Tokyo, Japan odaka-akihiro@fujielectric.com

Jun-ichi Itoh Nagaoka University of Technology Nagaoka, Niigata, Japan itoh@vos.nagaokaut.ac.jp

> Akio Toba Fuji Electric Co., Ltd. Tokyo, Japan toba-akio@fujielectric.com

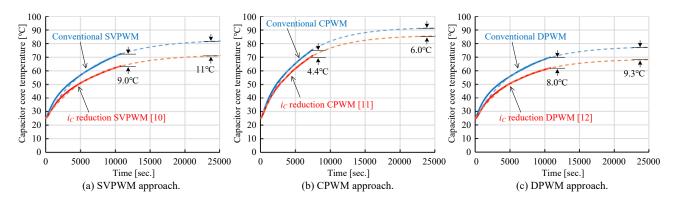

*Abstract*—This paper demonstrates the thermal stress reduction for the DC-link capacitors with multiple PWM strategies. An optimized positioning of the gate pulse reduces the DC-link capacitor current. The capacitor current reduction space vector PWM (SVPWM) strategies reduces the film capacitor core temperature by a maximum of 9.0°C compared to those obtained with the conventional strategies, whereas the maximum allowable temperature of the film capacitor is 105°C. The carrier-based PWM approaches also reduce the thermal stress; however, the reduction amount is not as large as the SVPWM approach. In addition to the trade-off between the implementation requirement and the reduction effect on the capacitor current, the analytical and experimental results confirm that there is a trade-off between the improved capacitor current harmonics and the worsened load current harmonics.

Keywords— Two-level voltage source inverter, DC-link capacitor, Thermal stress, PWM

## I. INTRODUCTION

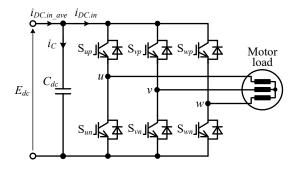

Three-phase AC motors are widely used in both industrial and household applications [1]–[5]. The employment of film capacitors in the DC-link part of the three-phase VSI have been actively researched to absorb the current ripple due to the inverter fast switching. The maximum allowable temperature of polypropylene, which is a dielectric material of the film capacitor, is 105°C [6]; thus, the suppression of its temperature rise is important. It is possible to suppress the temperature rise of the capacitors by reducing the harmonic components of DC-link current  $i_{DC.in}$ , defined in Fig. 1.

So far, several modulation strategies of PWM inverter have been proposed for the reduction of the current stress on the DC-link capacitors [7]–[12]. In several approaches based on space vector PWM (SVPWM), the capacitor current is minimized by selecting the optimized combination of the voltage space vectors [7]–[10]. On the other hand, with approaches based on triangular carrier-based PWM, threephase modulating signals which are shifted in every half control period also achieve the switching patterns for the capacitor current reduction [11]–[12]. Nevertheless, only the reduction effect of these PWM strategies on the capacitor current have been demonstrated in the past works, whereas the thermal stress for the DC-link capacitors with these strategies have not been evaluated yet.

This paper provides experimental evaluations and the comparison of the thermal stress for the DC-link capacitors with regard to the several PWM strategies by using the Satoru Fujita Fuji Electric Co., Ltd. Tokyo, Japan fujita-satoru@fujielectric.com

Hidetoshi Umida Fuji Electric Co., Ltd. Tokyo, Japan umida-hidetoshi@fujielectric.com

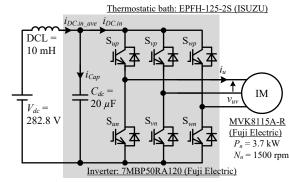

Fig. 1. Three-phase two-level VSI employed in motor drive system.

thermostatic bath, leading to fair comparisons. In addition, multilateral evaluations demonstrate that there is trade-off between the capacitor current and the output current harmonics, which can be the choice index of the capacitor current reduction PWM strategies.

This paper is organized as follows: first, the reduction methods of the DC-link capacitor current with the multiple PWM strategies are presented. Second, the effects on the DClink capacitor current, the output phase current, and the inverter efficiency are compared by analysis and experiment. Finally, the capacitor temperature rise test is presented to confirm the effectiveness of these capacitor current reduction PWM strategies.

# II. PWM STRATEGIES FOR DC-LINK CAPACITOR CURRENT REDUCTION

# A. SVPWM Approaches [7]–[10]

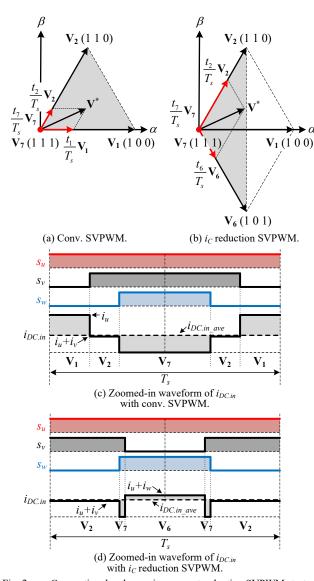

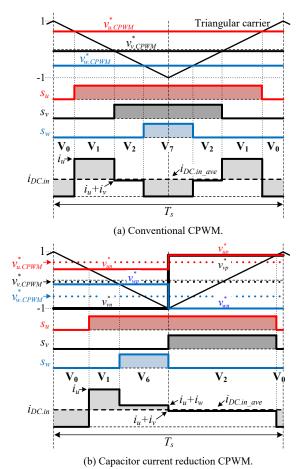

Fig. 2 shows the conventional and the capacitor current reduction SVPWM strategies at the modulation index (*m*) of 0.7, phase angle ( $\theta$ ) of 25 degrees, and the load power factor (cos  $\varphi$ ) of 0.866. Instantaneous value of the inverter input current is the superposition summation of the switched current pulses from each phase leg [13] and calculated as

$$i_{DC.in} = \sum_{x=u,v,w} \left( s_x \times i_x \right). \tag{1}$$

The capacitor current is calculated as difference between  $i_{DC.in}$  and its average value  $i_{DC.in\_ave}$  as following equation, and corresponds to the shaded areas in  $i_{DC.in}$  waveform [14].

Fig. 2. Conventional and capacitor current reduction SVPWM strategies at m = 0.7,  $\theta = 25$  deg.,  $\cos \varphi = 0.866$ . In low modulation index region, the two non-adjacent active vectors and one zero vector are used to reduce the capacitor current.

$$i_{C.RMS}(T_s) = \sqrt{i_{DC.in.RMS}^2(T_s) - i_{DC.in\_ave}^2}$$

and

$$\begin{cases} i_{DC.in.RMS}(T_s) = \sqrt{\frac{1}{T_s} \int_0^{T_s} i_{DC.in}^2 dt} \\ i_{DC.in\_ave} = \frac{3}{4} m \cdot I_m \cos \varphi \end{cases}$$

(2)

where  $T_s$  is the control period,  $I_m$  is the maximum value of the load current, and  $\varphi$  is the load power factor lagging angle. Under these conditions, the combination of one active vector (V<sub>6</sub>), one non-adjacent active vector (V<sub>2</sub>), and one zero vector (V<sub>7</sub>) suppresses the capacitor current to the minimum [9]–[10]. This is because this vector combination results in the omission of V<sub>1</sub> which cause the largest error between the instantaneous value (=  $i_u$ ) and average value of DC-link current.

Fig. 3 shows another example of the conventional and the capacitor current reduction SVPWM strategies at m = 1.0, i.e. higher modulation index. If the tip of the voltage reference vector  $\mathbf{V}^*$  does not belong to the triangle formed by the tips of

Fig. 3. Conventional and capacitor current reduction SVPWM strategies at m = 1.0,  $\theta = 25$  deg.,  $\cos \varphi = 0.866$ . In high modulation index region, the three consecutive active vectors are used to reduce the capacitor current.

three voltage space vectors ( $V_6$ ,  $V_2$ , and  $V_7$ ) shown in Fig. 2(b), the voltage reference vector cannot be generated by synthesizing these voltage space vectors. Under these conditions, the combination of three consecutive active vectors ( $V_6$ ,  $V_1$ , and  $V_2$ ) suppresses the capacitor current to the minimum [7]–[10]. In addition, the available areas with the three consecutive voltage space vectors are the same as those with conventional SVPWM. Therefore, the capacitor current reduction SVPWM strategy allows the same output voltage limitations as conventional SVPWM to be obtained. However, those gate pulse layout for the capacitor current reduction shown in Fig. 2(d) and Fig. 3(d) is not realized by using only one triangular-carrier. Therefore, the capacitor current reduction SVPWM leads to the requirement of high cost hardware such as field-programmable gate array (FPGA).

#### B. Carrier-based Continuous PWM Approach [11]

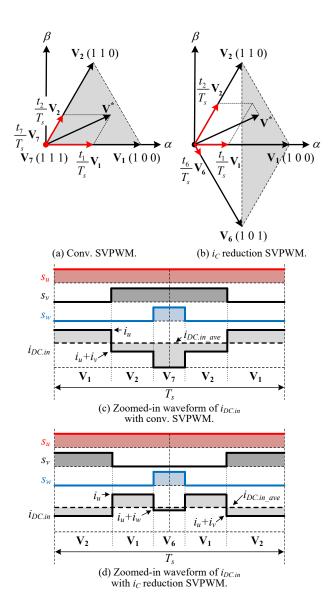

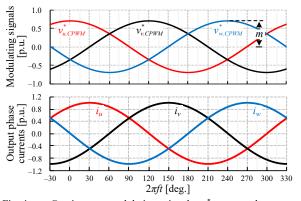

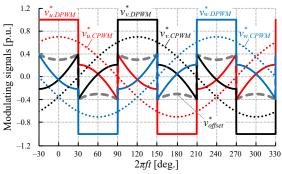

Fig. 4 shows the modulating signals of continuous PWM (CPWM) and output phase current at m = 0.7 and  $\cos \varphi = 0.866$ . The carrier-based PWM approaches generate the gate pulses by comparing the calculated modulating signals and the high-frequency carrier only with the general-purpose micro-

Fig. 4. Continuous modulating signals  $v_{xCPWM}^*$  and output phase currents  $i_x$  at m = 0.7 and  $\cos \varphi = 0.866$ .

computer, whereas the SVPWM approach requires FPGA. Generally, the modulating signals are set as the three-phase sinusoidal continuous waveforms as

$$\begin{cases} v_{u,CPWM}^* = m \cdot \cos\left(2\pi ft\right) \\ v_{v,CPWM}^* = m \cdot \cos\left(2\pi ft - 2\pi/3\right) \\ v_{w,CPWM}^* = m \cdot \cos\left(2\pi ft + 2\pi/3\right) \end{cases}$$

(3)

where m is the modulation index and f is the fundamental frequency.

The concept of the capacitor current reduction carrierbased PWM is realized under the premise that the modulating signals can be updated twice during one carrier cycle, which is the constraint of the micro-computer. By shifting the modulating signals in every half control period while maintaining its average value during a control period, only the gate pulse timings is adjusted while maintaining these widths. The positively-shifted modulating signal  $v_{xp}^*$  and the negatively-shifted modulating signal  $v_{xn}^*$  are calculated as

$$\begin{cases} v_{xp}^{*} = (2 - A_{x}) \cdot v_{x,CPWM}^{*} + A_{x} - 1 \\ v_{xn}^{*} = A_{x} \cdot (v_{x,CPWM}^{*} - 1) + 1 \end{cases} \quad (\text{if } v_{x,CPWM}^{*} \ge 0) \\ \begin{cases} v_{xp}^{*} = A_{x} \cdot (v_{x,CPWM}^{*} + 1) - 1 \\ v_{xn}^{*} = (2 - A_{x}) \cdot v_{x,CPWM}^{*} - A_{x} + 1 \end{cases} \quad (\text{if } v_{x,CPWM}^{*} < 0) \end{cases}$$

where  $A_x$  is the shifting coefficient between the original and shifted modulating signal. The value of  $A_x$  is defined from 1.0 to 2.0.  $A_x$  of 1.0 means that the modulating signal shift is not performed.  $A_x$  of 2.0 indicates that the modulating signal is shifted maximally in linear-modulation region.

Fig. 5 shows the zoomed-in waveforms of the modulating signals, the three-phase switching functions, and the inverter input current with the conventional and capacitor current reduction continuous PWM (CPWM) strategies. For the capacitor current reduction, firstly, *u*-phase modulating signal should become larger than the other two phase modulating signals, and the gate pulse  $s_u$  should cover  $s_v$  and  $s_w$  in the time domain to avoid the  $i_{DC.in}$  polarity flip compared to the  $i_{DC.in\_ave}$  polarity. Secondly, the overlap of the other two gate pulses  $s_v$  and  $s_w$  should be shortened to further reduce  $i_{DC.in\_ave}$ . With those modified gate pulse timings, the applying durations of  $V_1$  and  $V_7$ , which cause the large

Fig. 5. Zoomed-in waveforms of CPWM modulating signals, switching functions, and inverter input current at m = 0.7,  $\theta = 25$  deg.,  $\cos \varphi = 0.866$ . The divergence degree coefficients between the original voltage references and shifted references are set as  $A_u = 1.68$ ,  $A_v = 2.00$ , and  $A_w = 2.00$ .

difference between  $i_{DC.in}$  (=  $i_u$  with V<sub>1</sub>, or 0 with V<sub>7</sub>) and  $i_{DC.in\_ave}$ , are shortened and eliminated compared to the conventional CPWM. Furthermore, the applying durations of V<sub>2</sub> and V<sub>6</sub>, which result in the small  $i_{DC.in}$  harmonics, are extended and generated with those gate pulses. In order to achieve both the criterion for avoiding the  $i_{DC.in}$  polarity flip compared to the  $i_{DC.in\_ave}$  polarity and the criterion for reducing the  $i_{DC.in}$  fluctuation,

- 1)  $v_{u}^{*}$ , whose output phase current is positive, is shifted to the positive side simultaneously with the larger phase voltage reference between the other two phases, i.e.  $v_{v}^{*}$ .

- 2)  $v_v^*$  and  $v_w^*$  are shifted alternately and maximally to the positive side as long as they do not exceed  $v_{up}^*$  and  $v_{un}^*$ .

# C. Carrier-based Discontinuous PWM Approach [12]

Fig. 6 shows the modulating signals of discontinuous PWM (DPWM) and its injected zero sequence signal at m = 0.7. The discontinuous modulating signals lead to the advantages of the switching loss reduction due to the reduced switching transitions compared to those with CPWM. In addition, DPWM strategy extends the linear modulation range compared to CPWM. The discontinuous modulating signals are obtained by injecting the zero sequence signal  $v_{offset}^*$  into  $v_{x.CPWM}^*$  [15] as

$$v_{x,DPWM}^{*} = v_{x,CPWM}^{*} + v_{offset}^{*} (x = u, v, w),$$

$$v_{offset}^{*} = \begin{cases} 1 - |v_{max}| & (\text{if } |v_{max}| \ge |v_{min}|) \\ -1 + |v_{min}| & (\text{if } |v_{min}| < |v_{max}|) \end{cases},$$

$$\begin{cases} v_{max} = \max \left[ v_{u,CPWM}^{*}, v_{v,CPWM}^{*}, v_{w,CPWM}^{*} \right] \\ v_{min} = \min \left[ v_{u,CPWM}^{*}, v_{v,CPWM}^{*}, v_{w,CPWM}^{*} \right] \end{cases}.$$

(5)

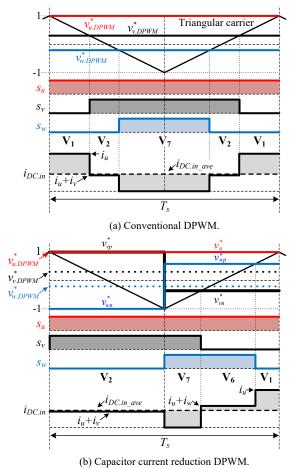

Fig. 7 shows the zoomed-in waveforms of the modulating signals, the three-phase switching functions, and the inverter input current with the conventional and capacitor current reduction DPWM strategies. In a similar way to the CPWM approach, shifted discontinuous modulating signals, calculated as following, are used to reduce the capacitor current in the DPWM approach.

$$\begin{cases} v_{xp}^{*} = 1 & \text{(if } v_{x.DPWM}^{*} \ge 0) \\ v_{xn}^{*} = 2 \cdot v_{x.DPWM}^{*} - 1 & \text{(if } v_{x.DPWM}^{*} \ge 0) \\ \begin{cases} v_{xp}^{*} = 2 \cdot v_{x.DPWM}^{*} - 1 & \text{(if } v_{x.DPWM}^{*} < 0). \end{cases} \end{cases}$$

(6)

For the capacitor current reduction, overlap period between two unclamped phases' switching functions,  $s_v$  and  $s_w$  in Fig. 7, should be shortened. Therefore, there two phase modulating signals  $v_{v,DPWM}^*$  and  $v_{w,DPWM}^*$  are shifted alternately to the positive side. As a result, the applying durations of V<sub>1</sub> and V<sub>7</sub>, which cause the large difference between  $i_{DC.in}$  and  $i_{DC.in\_ave}$ , are shortened and eliminated Instead of the omission of these worse switching periods for the capacitor current, the applying durations of V<sub>2</sub> and V<sub>6</sub>, which result in the small  $i_{DC.in}$ harmonics, are extended and generated just like CPWM approach shown in Fig. 5.

These carrier-based CPWM and DPWM approaches require only general-purpose micro-computer and FPGA is not necessary. However, the reduction effects on the capacitor current are inferior to the SVPWM approaches because the degree of freedom for the gate pulse timing is limited in the carrier-based PWM approaches. Therefore, the optimized gate pulse layout for the capacitor current reduction cannot be achieved in the carrier-based PWM approaches.

#### **III. ANALYTICAL RESULTS**

#### A. DC-link Capacitor RMS Current

As explained in above section, the DC-link capacitor RMS current is dependent on m,  $\varphi$ , and the switching patterns. The DC side of the three-phase VSI operates at six fold fundamental frequency; hence, the normalized DC-link capacitor RMS current is calculated based on (2) by considering only a sixth of the fundamental period as

$$I_{C.RMS(p.u.)} = \frac{1}{I_m} \sqrt{\frac{3}{\pi} \int_0^{\pi/3} \left( \sum \left[ \frac{t_k}{T_s} \left( i_{DC.in.k} - i_{DC.in\_ave} \right)^2 \right] \right) d\theta}$$

(7)

Fig. 6. Modulating signals of DPWM  $v_{x,DPWM}^*$  and its injected zero sequence  $v_{affset}^*$  signal at m = 0.7.

Fig. 7. Zoomed-in waveforms of DPWM modulating signals, switching functions, and inverter input current at m = 0.7,  $\theta = 25$  deg.,  $\cos \varphi = 0.866$ .

where  $t_k$  is the on-duty of VSI voltage space vector  $\mathbf{V}_{\mathbf{k}}$  ( $k = 0 \sim 7$ ) within  $T_s$ , and  $i_{DC ink}$  is the instantaneous DC-link current value with the voltage space vector  $\mathbf{V}_{\mathbf{k}}$ .

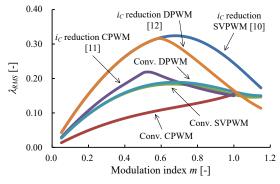

Fig. 8 shows the comparisons of the DC-link capacitor RMS current under the high load power factor conditions. Both figures confirm that there are no  $I_{C,RMS(p.u.)}$  differences between the conventional SVPWM, CPWM, and DPWM due to those same applying durations of the active vectors and the zero vectors. Fig. 8(a) confirms that the capacitor current reduction SVPWM leads to the best reduction effect in the modulation index region from 0.6 to 0.8 under the unity load power factor condition, which is a typical operating condition of the grid-tied VSI. Within the carrier-based PWM approaches, the capacitor current reduction DPWM leads to the better reduction effect compared to the CPWM approach.

Fig. 8.  $I_{CRMS(p,u.)}$  comparisons between conventional and capacitor current reduction PWM strategies against different modulation index at high load power factor conditions.

This is because the fact that certain one phase discontinuous modulating signal is always clamped, making it possible to set the switching pattern which leads to the smaller  $i_{DC.in}$  ripple longer than CPWM approach. Fig. 8(b) demonstrates the after-mentioned experimental condition of  $\cos \varphi = 0.891$  with an induction motor load. This trend in the reduction effect between the three capacitor current reduction PWM approaches is clearly shown also in this condition.

# B. Load Current Quality

In order to evaluate the load current quality, the concept of harmonic flux presented in [16] is used. Assuming that the motor switching frequency model is an inductance L, a harmonic flux load current vector  $\mathbf{I}_{\mathbf{h}}$  has a proportional relationship between the harmonic flux vector  $\lambda_{\mathbf{h}}$  (time integral of the instantaneous error voltage vector) as

$$\boldsymbol{\lambda}_{\mathbf{h}} = L \mathbf{I}_{\mathbf{h}} = \int_{NT_s}^{(N+1)T_s} \left( \mathbf{V}_{\mathbf{k}} - \mathbf{V}^* \right) dt.$$

(8)

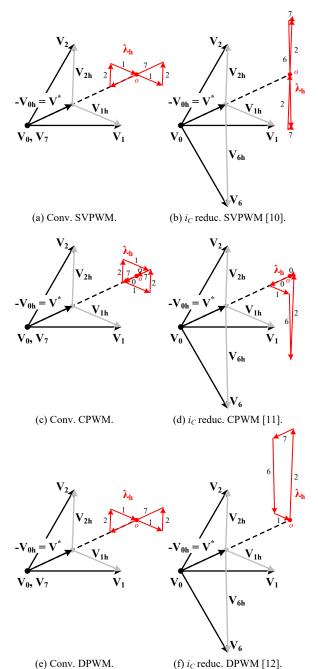

Fig. 9 shows the harmonic flux vector trajectories at m = 0.7,  $\theta = 25$  degrees. The distance between the trajectories and the origin (*o*), which is the initial value of  $\lambda_h$  at the beginning of the carrier cycle, corresponds to the magnitude of the harmonic flux [16]. The calculation of (8) and Fig. 9 evaluate the ripple current on a per-carrier cycle base. Since the harmonic flux vector characteristic has six-fold space symmetry, the per-fundamental cycle (per 60 degrees in space) harmonic flux RMS value, which characterizes the load current quality and the harmonic losses in the test motor, is calculated as follows.

Fig. 9. Harmonic flux vector  $\lambda_h$  trajectories at m = 0.7 and  $\theta = 25$  degrees. The distance between the trajectories and the origin (*o*), which is the initial value of  $\lambda_h$  at the beginning of the carrier cycle, corresponds to the magnitude of the harmonic flux.

$$\lambda_{RMS} = \sqrt{\frac{3}{\pi} \int_0^{\pi/3} \int_{NT_s}^{(N+1)T_s} \left\| \lambda_{\mathbf{h}} \right\|^2 dt d\theta}.$$

(9)

Fig. 10 shows the comparison of the harmonic flux RMS values Figs. 9–10 confirm that the capacitor current reduction PWM strategies worsen the harmonic flux compared to those obtained with each conventional PWM strategies. The reason is because the capacitor current reduction PWM strategies result in the application of the voltage space vector which is not the closes to  $V^*$ , i.e.  $V_6$  in Fig. 9. Within the capacitor current reduction PWM strategies, the SVPWM approach leads to the worst harmonic flux RMS value, and the carrier-based CPWM approach leads to the minimal deterioration.

This trend in the worsened harmonic flux RMS value with the capacitor current reduction PWM strategies is in a trade-off relationship with the trend in the improved DC-link capacitor RMS current which is shown in Fig. 8.

### IV. EXPERIMENTAL RESULTS

Fig. 11 shows the experimental setup. The DC-link capacitor and the inverter, operated at the switching frequency of 10 kHz, are placed inside thermostatic bath, whereas the temperature test starts from 25°C.

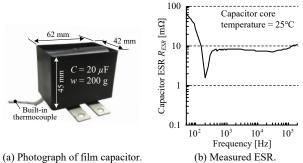

Fig. 12 shows the film capacitor under test as the DC-link capacitor. The thermocouple is built in the central part of the film capacitor. An equivalent series resistance (ESR) is measured using HIOKI 3532-50 LCR tester. At very low frequencies, ESR is high due to prevalent leakage. At low frequencies, ESR is dominated by the dielectric losses which decrease in inverse proportion to the frequency. At medium to high frequencies, the losses in the conductors are dominant and ESR becomes relatively constant. At high frequencies, ESR increases again due to the skin effect [17].

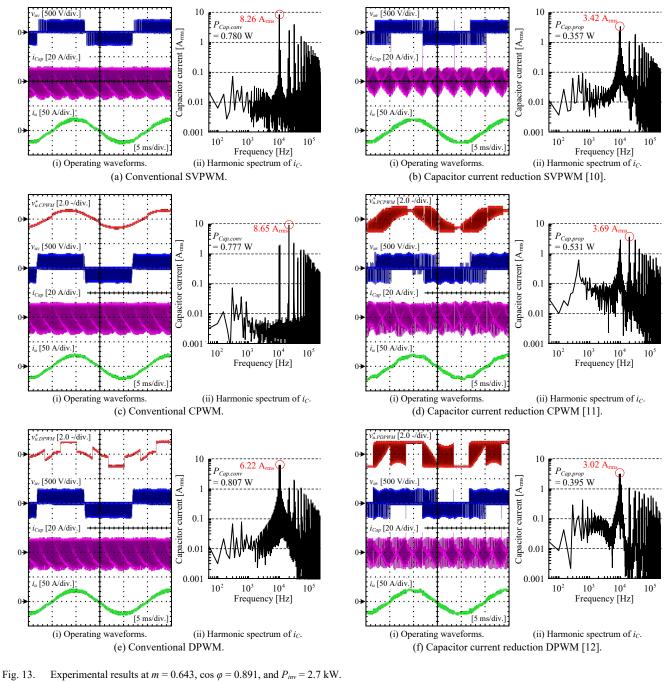

Fig. 13 shows the inverter operating test results with each modulation method. All capacitor current reduction PWM strategies reduce the switching frequency harmonics of the capacitor current compared to conventional strategies. Furthermore, the capacitor loss, which is calculated as follows, is also reduced.

$$P_{Cap} = \sum_{n=1} \left( R_{ESR.n} \cdot i_{Cap.n}^2 \right). \tag{10}$$

The maximum  $P_{Cap}$  reduction of 54.2% is obtained by the SVPWM approach as observed in Figs. 13(a)–(b). The reduction effects on  $P_{Cap}$  with the capacitor current reduction PWM strategies are correspond with the analytical results of  $I_{CRMS(p.u.)}$  shown in Fig. 8(b).

Fig. 14 shows the measured capacitor core temperature. The temperature tests are conducted until the bath internal temperature reached 60°C, the rated temperature of the coated vinyl of wire, under the same experimental conditions as in Fig. 13. The largest reduction of  $P_{Cap}$  with the SVPWM approach, which can be observed from Figs. 13(a)–(b), enables the greatest suppression of the capacitor core temperature rise. The application of the capacitor core temperature, which is estimated by the least-square method, by 11°C at most compared to the conventional strategy.

Table 1 lists the inverter efficiency with each PWM strategies under same experimental conditions as in Fig. 13. The CPWM strategies lead to the worst efficiency due to the requirement of more number of switching transitions. In addition, the SVPWM and DPWM strategies result in almost same efficiency because the number of switching transitions is same.

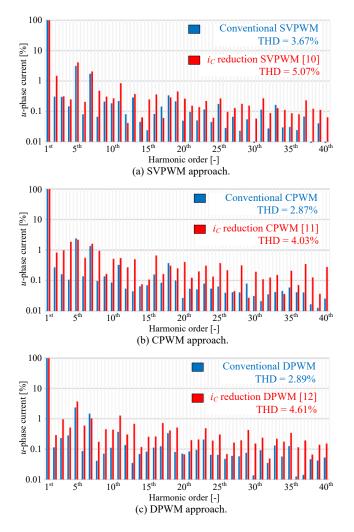

Fig. 15 shows the harmonic spectrum of  $i_u$  under the same experimental conditions as in Fig. 13. All capacitor current reduction PWM strategies worsen the phase current THD compared to the conventional PWM strategies because of the instantaneous error between the voltage reference vector and the output voltage vector. This trend is similar to the analytical results of  $\lambda_{RMS}$  shown in Fig. 10. In particular, the capacitor

Fig. 10. Comparison of harmonic flux RMS values  $\lambda_{RMS}$ .

Fig. 11. Experimental setup.

Fig. 12. Film capacitor under test.

current reduction SVPWM leads the largest time integral of the instantaneous voltage error and the worst current THD.

# V. CONCLUSION

This paper demonstrated the thermal stress reduction for the DC-link capacitors with multiple PWM strategies. The SVPWM approaches realized the optimal gate pulses for the capacitor current reduction with FPGA, and reduced the capacitor core temperature by 9.0°C at most compared to the conventional strategies. On the other hand, the optimal gate pulses generation led to the large instantaneous inverter voltage error; thus, the capacitor current and the output current harmonics have the trade-off relationship. The carrier-based PWM approaches, which do not require FPGA, realized the intermediate performances on the capacitor current and the output current harmonics between the conventional PWM strategies and the capacitor current reduction SVPWM.

Fig. 14. Measured capacitor core temperature and its approximated curves. The experimental conditions are at m = 0.643, cos  $\varphi = 0.891$ , and  $P_{inv} = 2.7$  kW, under same conditions in Fig. 13.

Fig. 15.  $i_u$  harmonic spectrum and its THD at m = 0.643,  $\cos \varphi = 0.891$ , under same conditions in Fig. 13.

TABLE I. MEASURED INVERTER EFFICIENCIES

|                   | Conv. | <i>i<sub>C</sub></i> reduction | Conv. | <i>i<sub>C</sub></i> reduction | Conv. | <i>i<sub>C</sub></i> reduction |

|-------------------|-------|--------------------------------|-------|--------------------------------|-------|--------------------------------|

|                   | SVPWM | SVPWM [10]                     | CPWM  | CPWM [11]                      | DPWM  | DPWM [12]                      |

| Efficiency<br>[%] | 96.11 | 96.39                          | 95.27 | 95.17                          | 96.30 | 96.22                          |

#### REFERENCES

- Ufot Ufot Ekong, M. Inamori, and M. Morimoto, "Field-Weakening Control for Torque and Efficiency Optimization of a Four-Switch Three-Phase Inverter-Fed Induction Motor Drive," *IEEJ J. Industry Applications*, vol. 8, no. 3, pp. 548–555, 2019.

- [2] A. Ura, M. Sanada, S. Morimoto, and Y. Inoue, "Influence of Structural Differences on Motor Characteristics of Concentrated Winding IPMSMs Obtained by Automatic Design," *IEEJ J. Industry Applications*, vol. 8, no. 3, pp. 458–464, 2019.

- [3] K. Abe, H. Haga, K. Ohishi, Y. Yokokura, and H. Kada, "Source Current Harmonics and Motor Copper Loss Reduction Control of Electrolytic Capacitor-less Inverter for IPMSM Drive," *IEEJ J. Industry Applications*, vol. 8, no. 3, pp. 404–412, 2019.

- [4] H. Sugimoto, I. Shimura, and A. Chiba, "Principle and Test Results of Energy-Saving Effect of a Single-Drive Bearingless Motor in Cooling Fan Applications," *IEEJ J. Industry Applications*, vol. 6, no. 6, pp. 456–462, 2017.

- [5] T. A. Huynh, and Min-Fu Hsieh, "Performance Evaluation of Interior Permanent Magnet Motors Using Thin Electrical Steels," *IEEJ J. Industry Applications*, vol. 6, no. 6, pp. 422–428, 2017.

- [6] Rubycon Corp., Japan. *Film Capacitor Technical Notes*. [Online]. Available: http://www.rubycon.co.jp/en/products/film/technote.html

- [7] J. Hobraiche, J.-P. Vilain, P. Macret, and N. Patin, "A New PWM Strategy to Reduce the Inverter Input Current Ripples," *IEEE Trans. Power Electron.*, vol. 24, no. 1, pp. 172–180, 2009.

- [8] A. M. Hava, and E. Ün, "A High-Performance PWM Algorithm for Common-Mode Voltage Reduction in Three-Phase Voltage Source Inverters," *IEEE Trans. Ind. Appl.*, vol. 26, no. 7, pp. 1998–2008, 2011.

- [9] T. D. Nguyen, N. Patin, and G. Friedrich, "Extended Double Carrier PWM Strategy Dedicated to RMS Current Reduction in DC-link Capacitors of Three-Phase Inverters," *IEEE Trans. Power Electron.*, vol. 29, no. 1, pp. 396–406, 2014.

- [10] K. Nishizawa, J. Itoh, A. Odaka, A. Toba, and H. Umida, "Current Harmonic Reduction Based on Space Vector PWM for DC-Link Capacitors in Three-Phase VSIs Operating Over a Wide Range of Power Factor," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4853– 4867, 2019.

- [11] K. Nishizawa, J. Itoh, S. Fujita, A. Odaka, A. Toba, and H. Umida, "Reduction of DC-link Current Harmonics over Wide Power-Factor Range for Three-Phase VSI using Single-Carrier-Comparison Continuous PWM," in *Conf. Proc. IEEE Energy Conversion Congress* and Exposition, pp. 6772–6779, 2018.

- [12] K. Nishizawa, J. Itoh, A. Odaka, A. Toba, and H. Umida, "Reduction of DC-link current harmonics for Three-phase VSI over Wide Power Factor Range using Single-Carrier-Comparison Discontinuous PWM," in *Conf. Proc. EPE'17 ECCE Europe*, vol. DS2c, no. 0297, 2017.

- [13] M. H. Bierhoff, and F. W. Fuchs, "DC-link Harmonics of Three-Phase Voltage-Source Converters Influenced by the Pulsewidth-Modulation Strategy—An Analysis," *IEEE Trans. Ind. Electron.*, vol. 55, no. 5, pp. 2085–2092, 2008.

- [14] T. Takeshita, "Output Voltage Harmonics Suppression of Matrix Converters Using Instantaneous Effective Values," in *Conf. Proc. IEEE Energy Conversion Congress and Exposition*, 270\_0839, 2010.

- [15] M. Depenbrock, "Pulse width control of a 3-phase inverter with nonsinusoidal phase voltages," in *IEEE-ISPC Conf. Rec.*, pp. 399–403, 1977.

- [16] A. M. Hava, R. J. Kerkman, and T. A. Lipo, "Simple Analytical and Graphical Methods for Carrier-Based PWM-VSI Drives," *IEEE Trans. Power Electron.*, vol. 14, no. 1, pp. 49–61, 1999.

- [17] TDK Corp., Japan. Film Capacitors General technical information. [Online]. Available: https://www.tdkelectronics.tdk.com/download/537974/480aeb04c789e45ef5bb968151 3474ba/pdf-generaltechnicalinformation.pdf